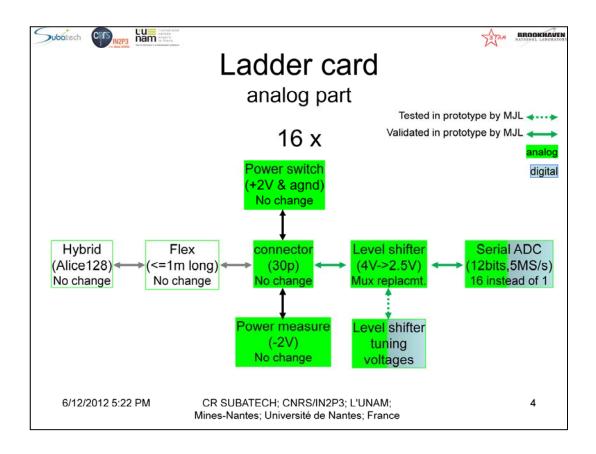

The only change (compared to old SSD) in the analog part is the ADC.

The 16 analog lines were multiplexed to 1 ADC.

Now, each analog line has a dedicated ADC.

The new ADC works at lower voltage, implying level shifting for the analog lines.

MJL tested Analog to Digital conversion of static voltages applied to the input connectors.

Level shifter showed bad rejection of analog power supplies due to Digital to Analog converter used as tunable voltage reference.

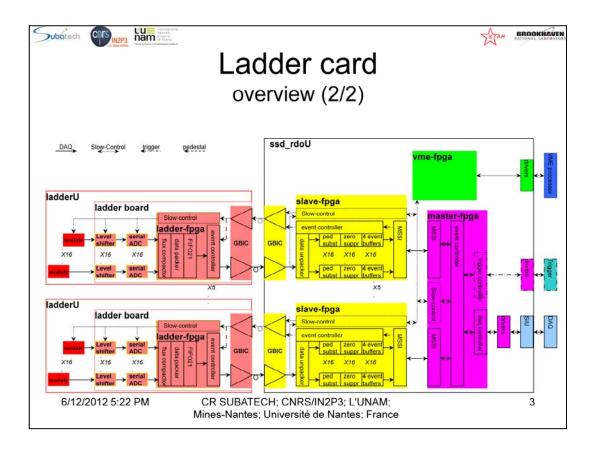

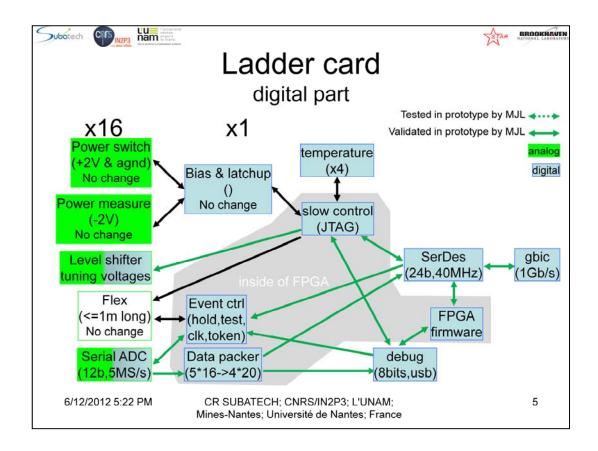

The digital part of the ladder board is mostly new, due to the changes

- from 1 to 16 ADC (now, we convert data from the 16 sensors at the same time),

- from parallel ADC to serial ADC

- from daisy chain copper bus to high speed serial optical line

MJL validated programming of FPGA firmware, slow-control and acquisition using both GBIC interface and debug interface.

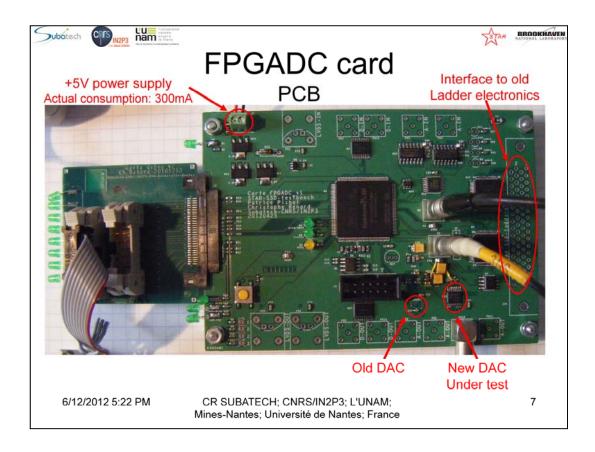

FPGADC\_v1 card will replace the old test bench that we used to test ladders equipped with the old electronics.

I added some components to test a new design for the DAC.

New firmware in FPGA to setup values in new DAC is working.

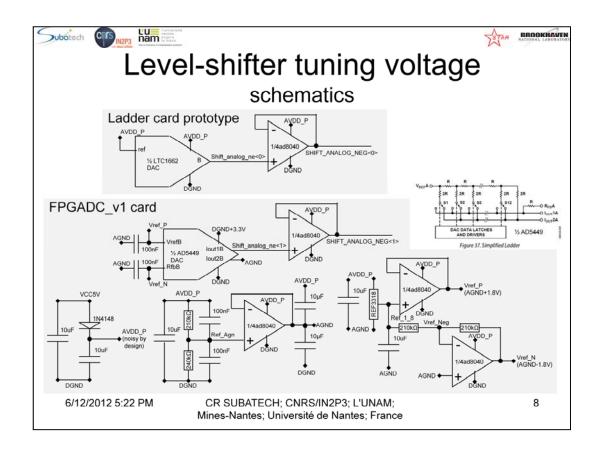

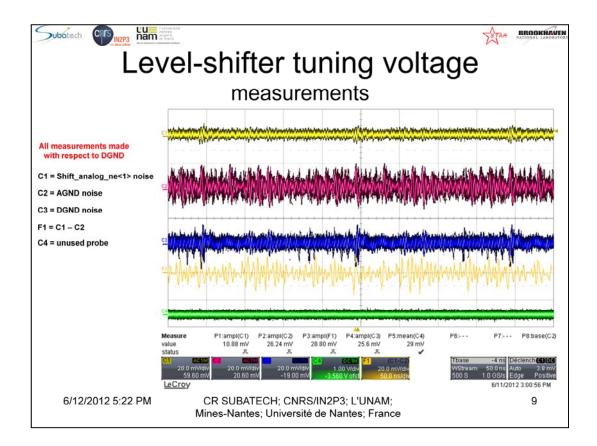

Ladder card prototype:

• Shift\_analog\_ne<0> referenced to DGND => copies -2V power supply variations

• Reference input of LTC1662 connected to +2V power supply => Shift\_analog\_ne<0> copies +2V power supply variations

FPGADC\_v1 card:

• Shift\_analog\_ne<1> referenced to AGND => independent from -2V power supply variations

• Reference inputs of AD5449 connected to Vref\_P and Vref\_N voltages => Shift\_analog\_ne<1> independent from +2V power supply variations

• AVDD\_P intentionally made noisy to see how Shift\_analog\_ne<1> rejects this noise

Abnormal noise on AGND comes mainly from bad decoupling on FPGADC card. More tests needed to validate (or reject) new design.

| Subatech                                                                                            |                                                                                                                                 |

|-----------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|

| Ladder card                                                                                         |                                                                                                                                 |

|                                                                                                     | options (1/2)                                                                                                                   |

| Fabrication options:                                                                                |                                                                                                                                 |

| 1.                                                                                                  | Fabricate few pre-prod now. Populate them for tests.<br>Then fabricate prod, taking test results into account.                  |

| 2.                                                                                                  | Fabricate full prod now but populate only few for tests.<br>Eventually fabricate new prod, taking test results into<br>account. |

| DAC options:                                                                                        |                                                                                                                                 |

| a)                                                                                                  | Keep actual DAC (LT1662) as-is                                                                                                  |

| b)                                                                                                  | Keep actual DAC (LT1662) but use a +1.8V voltage reference instead of +2V supply at the reference input.                        |

| c)                                                                                                  | Use new DAC (AD5449)                                                                                                            |

| 6/12/2012 5:22 PM CR SUBATECH; CNRS/IN2P3; L'UNAM; 10<br>Mines-Nantes; Université de Nantes; France |                                                                                                                                 |

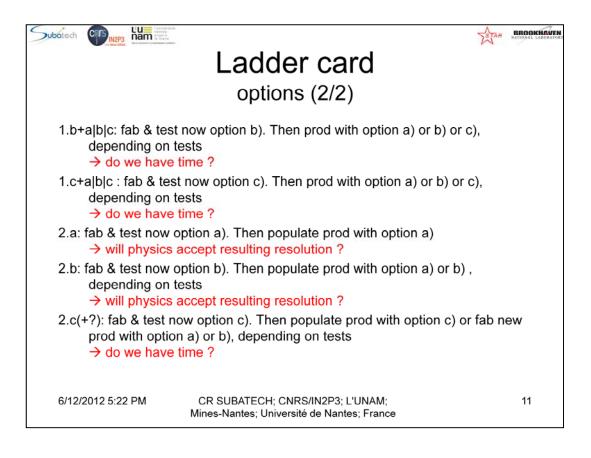

- 1. is preferred by Jim.

- $\rightarrow$  safe

- $\rightarrow$  slow (?): each fab takes ~2 months (including paperwork)

- 2. Is proposed (preferred?) by Micheal

- $\rightarrow$  gamble on test results

- $\rightarrow$  (could be) fast: saves one fab (~2 months)

- a)

- → ready now

- $\rightarrow$  will physics accept resulting resolution ?

- b)

- $\rightarrow$  almost ready now

- $\rightarrow$  easy to reverse to a)

- $\rightarrow$  will physics accept resulting resolution ?

- c)

- ightarrow needs time to validate, then implement in design

Many thanks for your attention