# **SSD** electronics review

M. LeVine BNL

M.J. LeVine BROOKHRAVEN

BROOKHAVEN

NATIONAL LABORATORY

M.J. LeVine

# Quick overview of upgrade

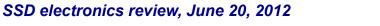

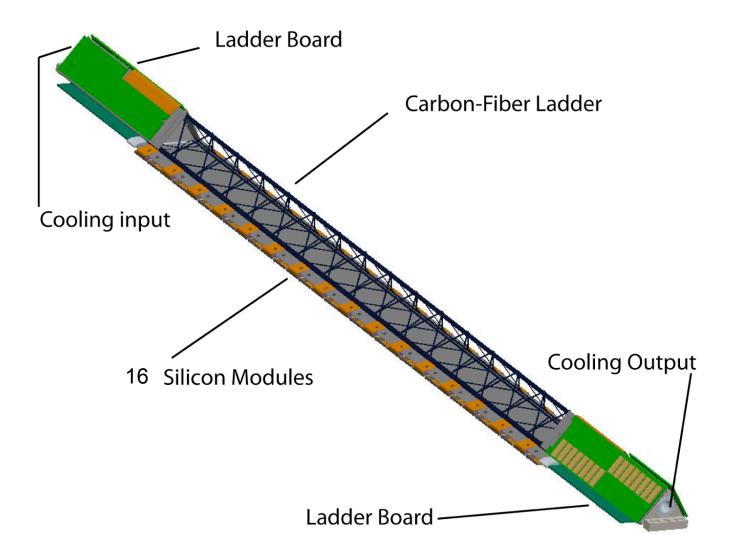

## SSD ladder

BROOKHAVEN NATIONAL LABORATORY

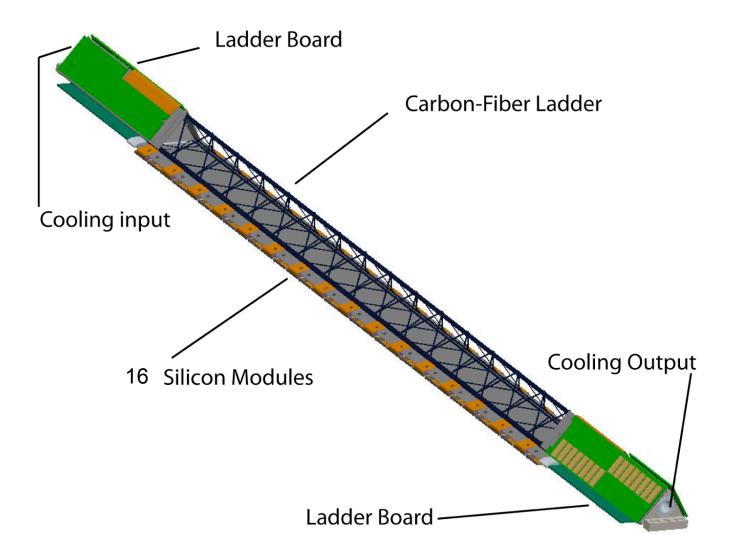

# Previous readout configuration

- Reading out front end:

- Replace single ADC with 16 ADCs

- digitize 16 modules in parallel

- Increase sampling rate to 5.00 MHz

- All ladders processed concurrently

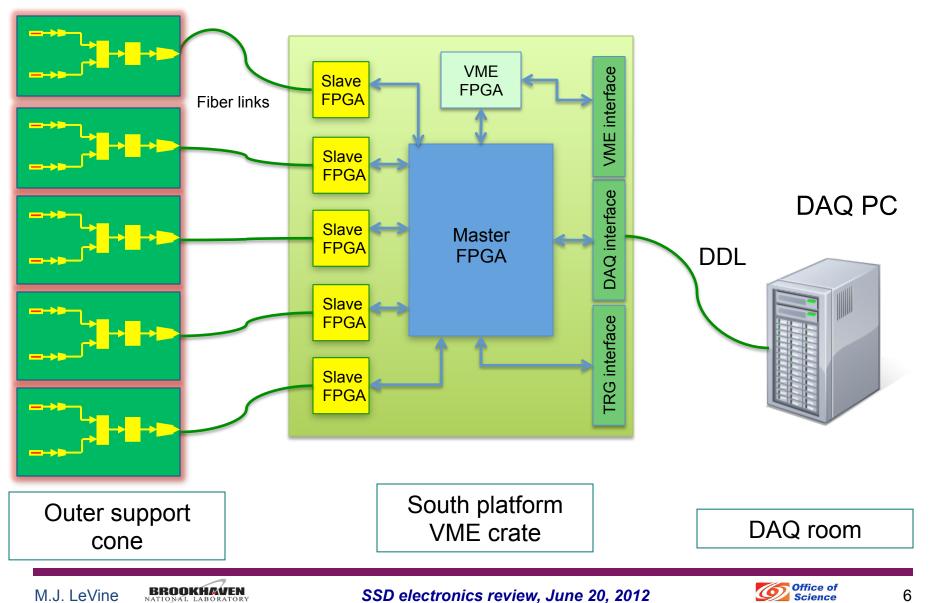

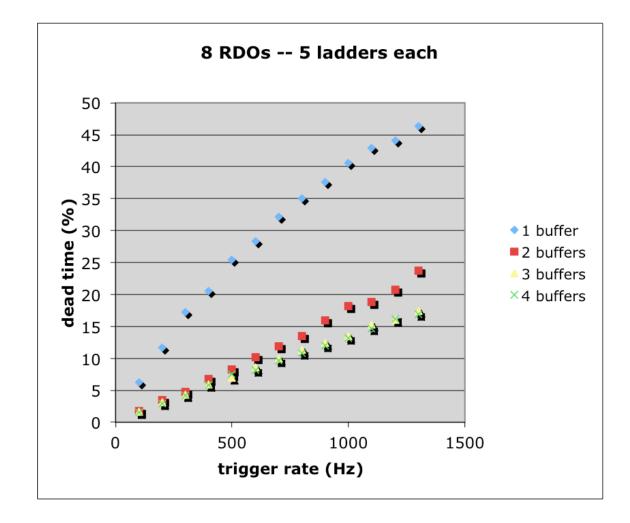

- Transferring data to PC

- Increase link throughput to DAQ PC to 120 Mbyte/s per 5 ladders

- 1850 µs -> 450 µs

- Multiple (derandomizing) buffers effectively hides this time

- Dead time: 10%@750Hz, <2%@100Hz

- [*cf*. existing: >80%@750Hz,30% @ 100Hz]

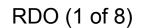

# Readout components

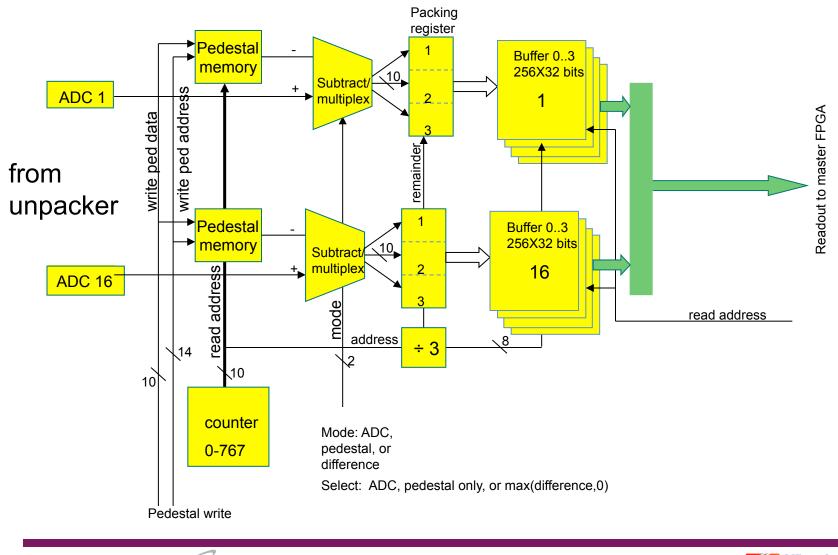

Ladder cards

## non zero-suppressed

- 3 10-bit ADC values to a 32-bit word

- Fixed order: position in buffer/word -> geographical position of strip

## zero suppressed

- Only strips with ADC value above threshold are present

- ADC value (10 bits) + strip location (14 bits)

- One strip per 32-bit word

- Alleviates large memory access burden on DAQ PC

- Doing this in real time in FPGA is simple

# **STAR** Dead time calculation - no zero suppression

## **STARead time calculations** – zero suppression

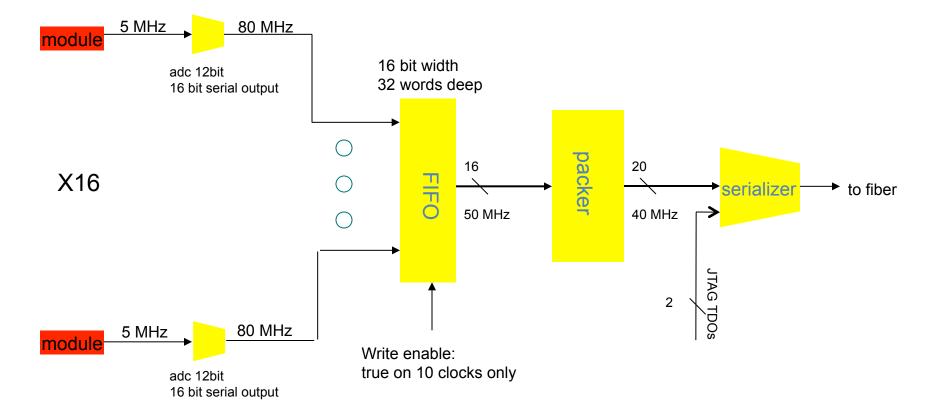

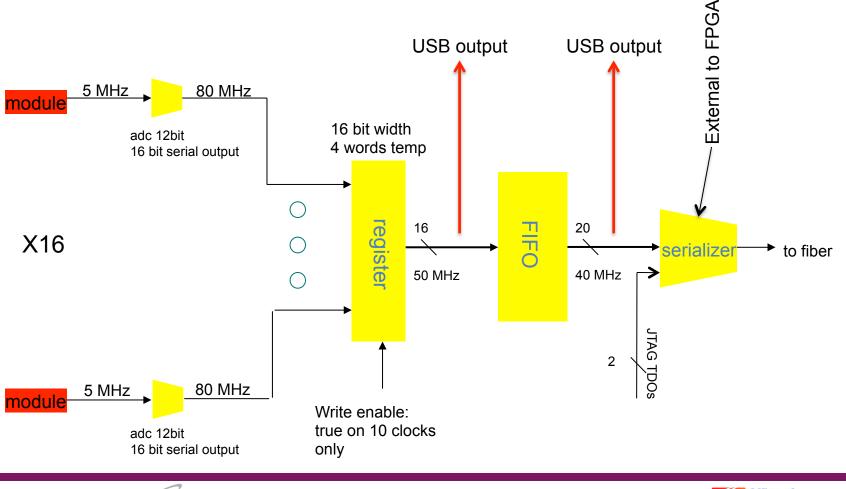

## Ladder data path

#### 1 set of adc samples: 10 X 16 bits => repacked into: 2 X 4 X 20 bits

M.J. LeVine

BROOKHAVEN NATIONAL LABORATORY

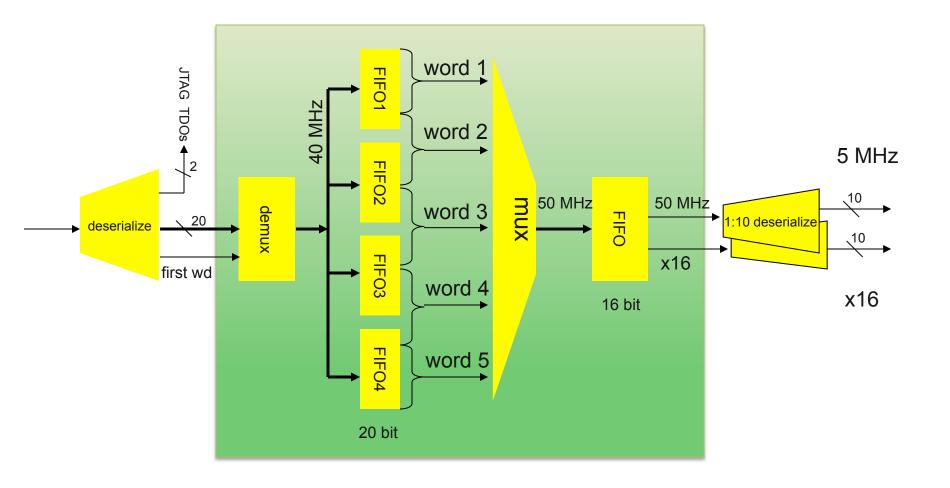

## **RDO slave - unpacker**

#### unpacking 4 20-bit words to 5 16-bit words

BROOKHAVEN

# Slave FPGA – ADC processing

(no zero suppression)

M.J. LeVine

BROOKHAVEN National laboratory

# Prototype ladder card testing

13

M.J. LeVine **BROOKHAVEN**

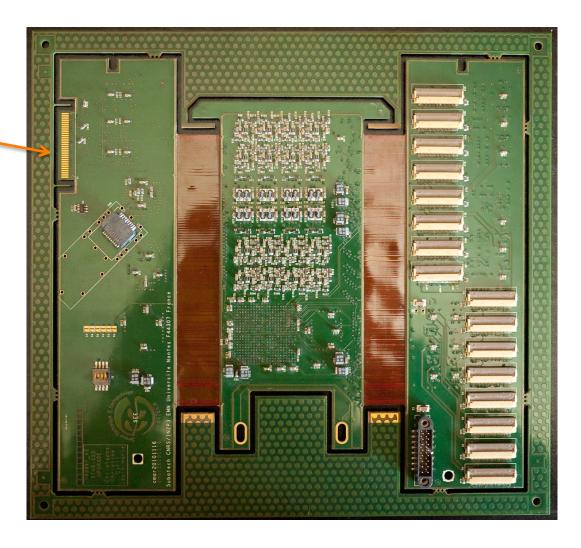

# Ladder board: (inside)

Flex circuit layer Frame cut loose when board is ready for ---installation

BROOKHAVEN

# Ladder board: (outside)

Edge connector for debug card

BROOKHAVEN NATIONAL LABORATORY

M.J. LeVine

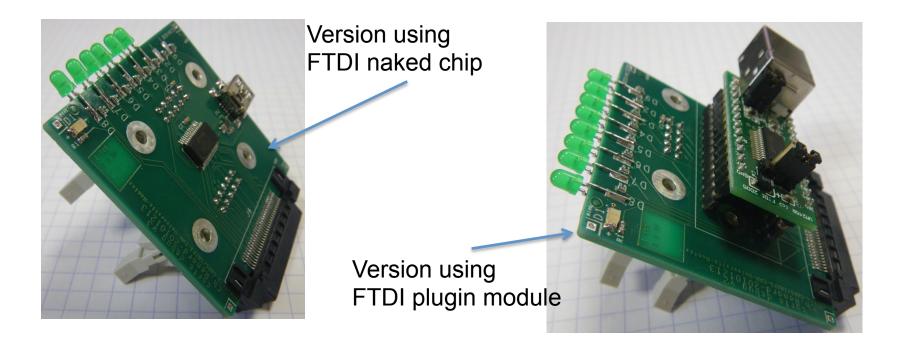

# Debug card (via edge connector)

Provides:

- JTAG header to configure FPGA

- JTAG header for slow controls

Both will be provided via fiber

- USB access to FPGA

## **USB** test results

| Number of devices is 2                            | pcBufRe |

|---------------------------------------------------|---------|

| ==== Device 0 is Subatech DbgV3n1 ======          | pcBufRe |

| Serial # A7U3EQBC                                 | pcBufRe |

|                                                   | pcBufRe |

| 1) sending the following bytes                    | pcBufRe |

| 0x41 0x41 0xFF 0xFF 0x42 0x42 0x00 0x00 0x43 0x43 | pcBufRe |

| 0xFF 0xFF 0x44 0x44 0x44 0x44                     | pcBufRe |

|                                                   | pcBufRe |

| 2) sending the following bytes                    | pcBufRe |

| 0x41 0x41 0xFF 0xFF 0x42 0x42 0x00 0x00 0x43 0x43 | pcBufRe |

| 0xFF 0xFF 0x44 0x44 0x44 0x44                     | pcBufRe |

|                                                   | pcBufRe |

| FT_Read = 32                                      | pcBufRe |

| pcBufRead[0] = 0x41<br>pcBufRead[1] = 0x41        | pcBufRe |

| pcBufRead[2] = 0x41<br>pcBufRead[2] = 0xFF        | pcBufRe |

| pcBufRead[2] = 0xFF                               | pcBufRe |

| pcBufRead[4] = 0x42                               | pobulik |

| pcBufRead[5] = 0x42                               |         |

| pcBufRead[6] = 0x00                               | Closed  |

| pcBufRead[7] = 0x00                               | Closed  |

| pcBufRead[8] = 0x43                               |         |

| pcBufRead[9] = 0x43                               |         |

| pcBufRead[10] = 0xFF                              |         |

| pcBufRead[11] = 0xFF                              |         |

| pcBufRead[12] = 0x44                              |         |

| pcBufRead[13] = 0x44                              |         |

| pcBufRead[14] = 0x44                              |         |

| pcBufRead[15] = 0x44                              |         |

ead[16] = 0x41 ead[17] = 0x41 ead[18] = 0xFF ead[19] = 0xFF ead[20] = 0x42ead[21] = 0x42ead[22] = 0x00 ead[23] = 0x00 ead[24] = 0x43 ead[25] = 0x43 ead[26] = 0xFF ead[27] = 0xFF ead[28] = 0x44 ead[29] = 0x44 ead[30] = 0x44 ead[31] = 0x44

Closed device A7U3EQBC

# **Slow controls JTAG signals**

| <b>T</b> |                                     |                                                              |                         |      |

|----------|-------------------------------------|--------------------------------------------------------------|-------------------------|------|

|          | Program te composition and a second | at data da ana da ata da | <del>un yana ungi</del> | TDO  |

|          |                                     |                                                              |                         | TDI  |

|          |                                     |                                                              |                         |      |

|          |                                     |                                                              |                         | тск⁴ |

|          |                                     |                                                              |                         |      |

|          |                                     |                                                              | i<br>i                  | TMS  |

reading register 0x01 ROBOCLKS: 0xaa 0xaa 0xaa 🖌 reading register 0x02 STATUS : 0x3e 0x60 0x3f reading register 0x03 CONFIG : 0x00 0x00 reading register 0x04 DAC VALS: 0x0a 0xa9 0x55 🖌 reading register 0x07 HYBRIDS : 0x00 0x00 reading register 0x08 LATCHUP : 0x00 reading register 0x09 RALLUMAG: 0x00 0x00 reading register 0x0b BYPASS : 0x00 0x00 reading register 0x0c VERSION : 0x26 0x01 0x20 0x11 ✔ reading register 0x0e TEMPS : 0x00 0x00 0x00 0x00 0x00 0x00

reading register 0x1b IDENTITE: 0xb7 🖌

Register with known content at startup

## Ladder response vs clock frequency

4.3 MHz

Fig 6: 6.0 MHz clock. Pedestal mean= - 447mV, S.D. = 8.8mV. Peak (cursor 2) mean= 114mV, S.D. = 8.8mV.

Horiz:100 ns/cm

6.0 MHz

5.0 MHz

#### M.J. LeVine

BROOKHAVEN NATIONAL LABORATORY

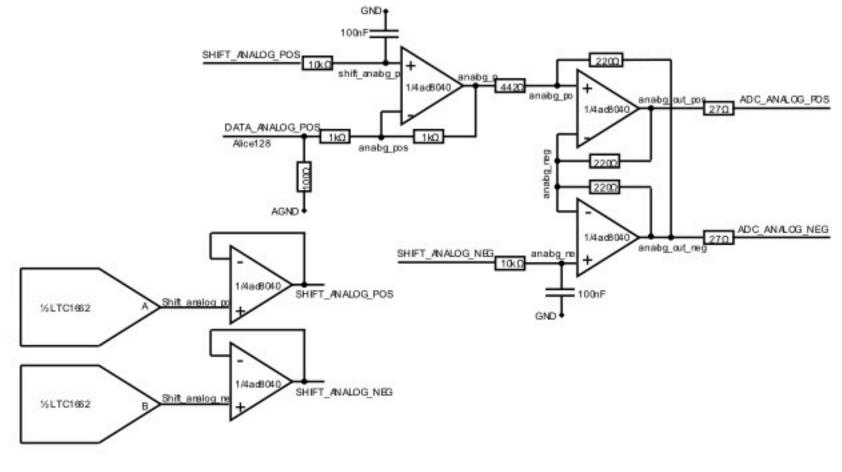

## Level-shifting for bias side

**DOE HFT Review**

BROOKHAVEN

NATIONAL LABORATORY

Ionizing radiation causes single bit errors in configuration memory (internal to FPGA)

– Change FPGA behavior

- Scale from observed error frequency in TOF

Estimate 1 error per 10 minutes in SSD

- Must pro-actively detect these errors by running CRC checks while acquiring data

– Provided by Altera

• Time to reconfigure FPGA: < 1 sec

## Fake static source

BROOKHAVEN NATIONAL LABORATORY

SSD electronics review, June 20, 2012

23

- Use USB to trigger ADC conversion, gather data

- Use "static fake ladder" to provide selectable DC level at each ladder input

- Allows verification of basic functionality of analog section

- Use "dynamic fake ladder" (in design) to verify ADC timing for each ladder.

- Use QRDO (in layout) to verify ladder card functionality up through fiber link

#### DOE HFT Review

M.J. LeVine

- Software

- Python script driving

- Multiple .exe (C code)

- Time to map response for 1 ADC: 30 sec

- Time to map all 16 ADCs: 20 minutes

Disconnect/connect flex cable

- Basis for future slow controls software

- SC uses JTAG header on debug card

Will be replaced by fiber protocol

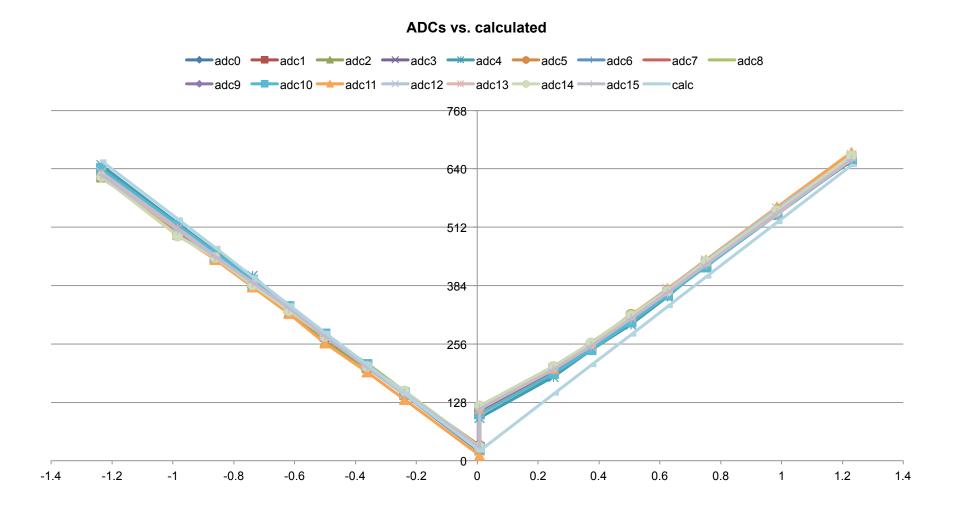

# Analog response for all ADCs

STAR

BROOKHAVEN

NATIONAL LABORATORY

M.J. LeVine

- Non-linear behavior of N-face not yet understood

- Discovered we are sensitive to PS fluctuations via DAC

- Will be separately regulated in production version (prototype in test)

# Verification of packing code

USB output for ADC data

BROOKHAVEN

NATIONAL LABORATOR

M.J. LeVine

Install USB spy at output of FIFO

SSD electronics review, June 20, 2012

Science

M.J. LeVine

- Following 4 slides are identical except for notation showing which bits are to be extracted for each word sent to the FIFO

- Lines FIFO[0]...FIFO[7] show the 21-bit word exiting the FIFO

SSD electronics review, June 20, 2012

Comparison shows that the packer is functioning correctly

DAC A = 300, DAC B = 500

|                                                                                                                                                                                                                      | , -                                                                                                                 |                                                                                                                                                       | bit<br>9                                                                                        | bit<br>0 |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|----------|

| ADC[15]:<br>ADC[14]:<br>ADC[13]:<br>ADC[12]:<br>ADC[11]:<br>ADC[10]:<br>ADC[10]:<br>ADC[9]:<br>ADC[9]:<br>ADC[9]:<br>ADC[8]:<br>ADC[7]:<br>ADC[6]:<br>ADC[6]:<br>ADC[5]:<br>ADC[4]:<br>ADC[3]:<br>ADC[1]:<br>ADC[1]: | 529<br>885<br>889<br>891<br>901<br>893<br>888<br>136<br>887<br>890<br>886<br>901<br>888<br>888<br>888<br>891<br>892 | 0x211<br>0x375<br>0x379<br>0x37B<br>0x385<br>0x37D<br>0x378<br>0x378<br>0x377<br>0x37A<br>0x376<br>0x376<br>0x378<br>0x378<br>0x378<br>0x378<br>0x378 | 1 1 (<br>1 1 ( | 01111011 |

Bit 20 ("first word") FIFO[0] 0x1FFEFF FIFO[1] 0x0107EF FIFO[2] 0x06EF09 FIFO[3] 0x076EF7 FIFO[4] 0x1FF6EF FIFO[5] 0x0B1374 FIFO[6] 0x00E24C FIFO[7] 0x0FC921

Fifo 0 (19..16) Fifo 0 (15..0)

DAC A = 300, DAC B = 500

|          |     |       | bit     | bit              |

|----------|-----|-------|---------|------------------|

|          |     |       | 9       | 0                |

|          |     |       | ======= | ================ |

| ADC[15]: | 529 | 0x211 | 1000    | 010001           |

| ADC[14]: | 885 | 0x375 | 1 1 0 1 | 110101           |

| ADC[13]: | 889 | 0x379 | 1 1 0 1 | 111001           |

| ADC[12]: | 891 | 0x37B | 1 1 0 1 | 111011           |

| ADC[11]: | 901 | 0x385 | 1 1 1 0 | 000101           |

| ADC[10]: | 893 | 0x37D | 1 1 0 1 | 111101           |

| ADC[9]:  | 888 | 0x378 | 1 1 0 1 | 111000           |

| ADC[8]:  | 136 | 0x088 | 0010    | 001000           |

| ADC[7]:  | 887 | 0x377 | 1 1 0 1 | 110111           |

| ADC[6]:  | 890 | 0x37A | 1 1 0 1 | 111010           |

| ADC[5]:  | 886 | 0x376 | 1 1 0 1 | 110110           |

| ADC[4]:  | 901 | 0x385 | 1 1 1 0 | 000101           |

| ADC[3]:  | 888 | 0x378 | 1101    | 111000           |

| ADC[2]:  | 888 | 0x378 | 1101    | 111000           |

| ADC[1]:  | 891 | 0x37B | 1101    | 111011           |

| ADC[0]:  | 892 | 0x37C | 1101    | 111100           |

| Bit 20<br>word" | ) ("first<br>') ↓ |

|-----------------|-------------------|

| FIFO[0]         | 0x1FFEFF          |

| FIFO[1]         | 0x0107EF          |

| FIFO[2]         | 0x06EF09          |

| FIFO[3]         | 0x076EF7          |

| FIFO[4]         | 0x1FF6EF          |

| FIFO[5]         | 0x0B1374          |

| FIFO[6]         | 0x00E24C          |

| FIFO[7]         | 0x0FC921          |

Fifo 1 (19..12) Fifo 1 (11..0)

DAC A = 300, DAC B = 500

|          |     |       | bit     | bit    |

|----------|-----|-------|---------|--------|

|          |     |       | 9       | 0      |

|          |     |       | ======= |        |

| ADC[15]: | 529 | 0x211 | 1000    | 010001 |

| ADC[14]: | 885 | 0x375 | 1101    |        |

| ADC[13]: | 889 | 0x379 | 1101    | 111001 |

| ADC[12]: | 891 | 0x37B | 1101    | 111011 |

| ADC[11]: | 901 | 0x385 | 1110    | 000101 |

| ADC[10]: | 893 | 0x37D | 1101    | 111101 |

| ADC[9]:  | 888 | 0x378 | 1101    | 111000 |

| ADC[8]:  | 136 | 0x088 | 0010    | 001000 |

| ADC[7]:  | 887 | 0x377 | 1101    | 110111 |

| ADC[6]:  | 890 | 0x37A | 1101    | 111010 |

| ADC[5]:  | 886 | 0x376 | 1101    | 110110 |

| ADC[4]:  | 901 | 0x385 | 1110    | 000101 |

| ADC[3]:  | 888 | 0x378 | 1101    | 111000 |

| ADC[2]:  | 888 | 0x378 | 1101    |        |

| ADC[1]:  | 891 | 0x37B | 1101    | 111011 |

| ADC[0]:  | 892 | 0x37C | 1101    | 111100 |

| Bit 20<br>word") |                        |

|------------------|------------------------|

| FIFO[0]          | 0x1FFEFF               |

| FIFO[1]          | 0x0107EF               |

| FIFO[2]          | 0x0 <mark>6EF09</mark> |

| FIFO[3]          | 0x076EF7               |

| FIFO[4]          | 0x1FF6EF               |

| FIFO[5]          | 0x0B1374               |

| FIFO[6]          | 0x00E24C               |

| FIFO[7]          | 0x0FC921               |

|                  |                        |

Fifo 2 (19..8) Fifo 2 (7..0)

DAC A = 300, DAC B = 500

|          |     |       | bit     | bit          |

|----------|-----|-------|---------|--------------|

|          |     |       | 9       | 0            |

|          |     |       | ======= | ============ |

| ADC[15]: | 529 | 0x211 | 1000    | 010001       |

| ADC[14]: | 885 | 0x375 | 1101    | 1 1 0 1 0 1  |

| ADC[13]: | 889 | 0x379 | 1101    | 111001       |

| ADC[12]: | 891 | 0x37B | 1101    | 1 1 1 0 1 1  |

| ADC[11]: | 901 | 0x385 | 1110    | 00101        |

| ADC[10]: | 893 | 0x37D | 1101    | 1 1 1 1 0 1  |

| ADC[9]:  | 888 | 0x378 | 1101    | 111000       |

| ADC[8]:  | 136 | 0x088 | 0010    | 001000       |

| ADC[7]:  | 887 | 0x377 | 1101    | 1 1 0 1 1 1  |

| ADC[6]:  | 890 | 0x37A | 1101    | 111010       |

| ADC[5]:  | 886 | 0x376 | 1101    | 1 1 0 1 1 0  |

| ADC[4]:  | 901 | 0x385 | 1110    | 00101        |

| ADC[3]:  | 888 | 0x378 | 1101    | 111000       |

| ADC[2]:  | 888 | 0x378 | 1101    | 111000       |

| ADC[1]:  | 891 | 0x37B | 1101    | 1 1 1 0 1 1  |

| ADC[0]:  | 892 | 0x37C | 1101    | 111100       |

| Bit 20<br>word") | ` •      |

|------------------|----------|

| FIFO[0]          | 0x1FFEFF |

| FIFO[1]          | 0x0107EF |

| FIFO[2]          | 0x06EF09 |

| FIFO[3]          | 0x076EF7 |

| FIFO[4]          | 0x1FF6EF |

| FIFO[5]          | 0x0B1374 |

| FIFO[6]          | 0x00E24C |

| FIFO[7]          | 0x0FC921 |

|                  |          |

Fifo 3 (19..4) Fifo 3 (3..0)

- Routing error on FPGA discovered

- Temporary fix using interposer

- Continue testing using original PCB w/ interposer

- Configure FPGA via debug card JTAG header

- Communication with FPGA via USB verified

- Slow controls functionality (JTAG) verified

- Testing of ladder card has exposed only 2 problems

- FPGA orientation

- Corrected on pre-production version

- Susceptibility of analog section to PS variation

- Can degrade ability to interpolate centroid

- Alternate DAC design being tested

- To be done

- Verify interaction with ladder modules

- Token passing

- JTAG

M.J. LeVine

RROOKHAVEN

- All functions that have been tested are working correctly

- Remaining to verify –

– JTAG to ladder components

- Tests of Avago xcvr show that it dies around 100 kRad (Co<sup>60</sup> source)

- A rad hard version has been developed for LHC

- Working prototypes now available

- Almost plug compatible with Avago

- Requires 2.5V instead of 3.3V

- Jumper provided on ladder board to select 2.5V supply

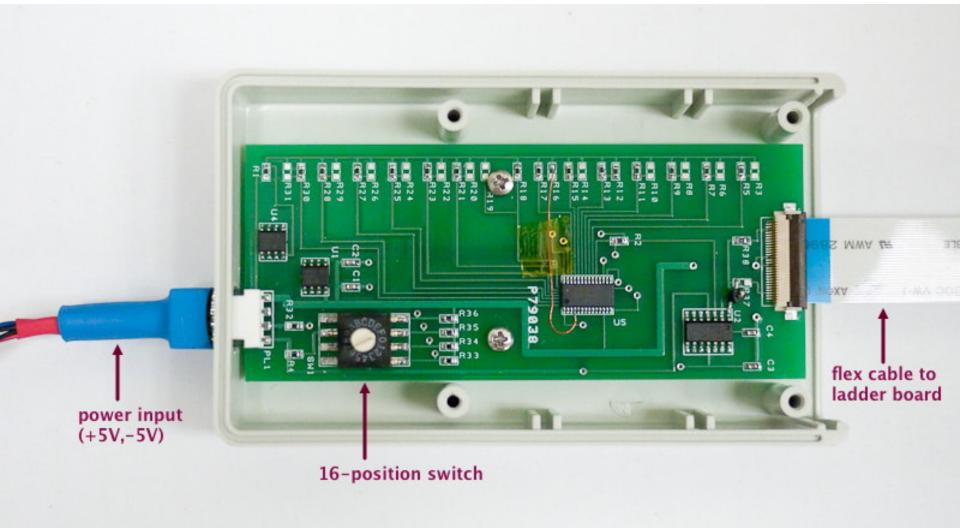

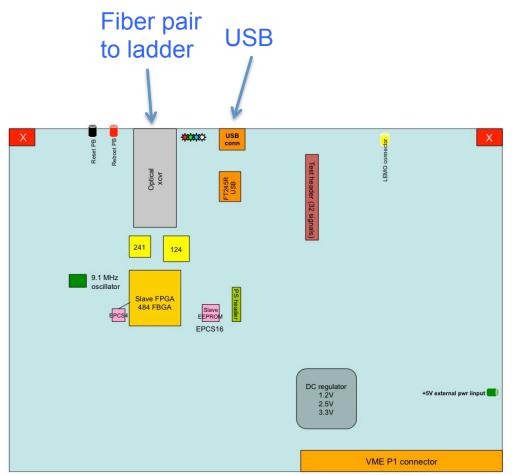

# QRDO -

BROOKHAVEN

NATIONAL LABORATOR

M.J. LeVine

- prototype RDO slave

- ladder card test stand

#### **QRDO** (Fast-track version of RDO)

- Interfaces to one ladder board

- Implements one slave FPGA

- Only features required for testing ladder board

- No TRG, DAQ

- All input/output via USB

- Can acquire up to 4 events at full speed

BROOKHAVEN

NATIONAL LABORATOR

M.J. LeVine

+5V, GND only

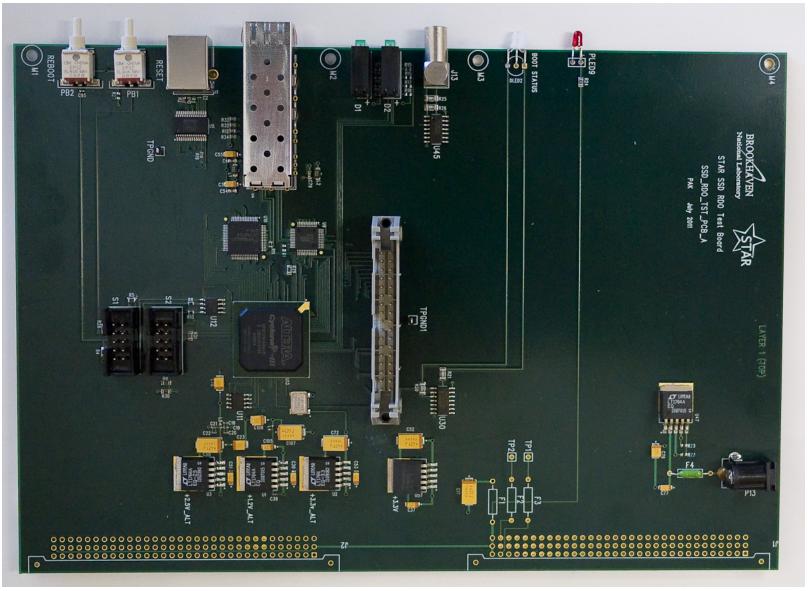

#### **QRDO** assembled

M.J. LeVine

BROOKHAVEN NATIONAL LABORATORY

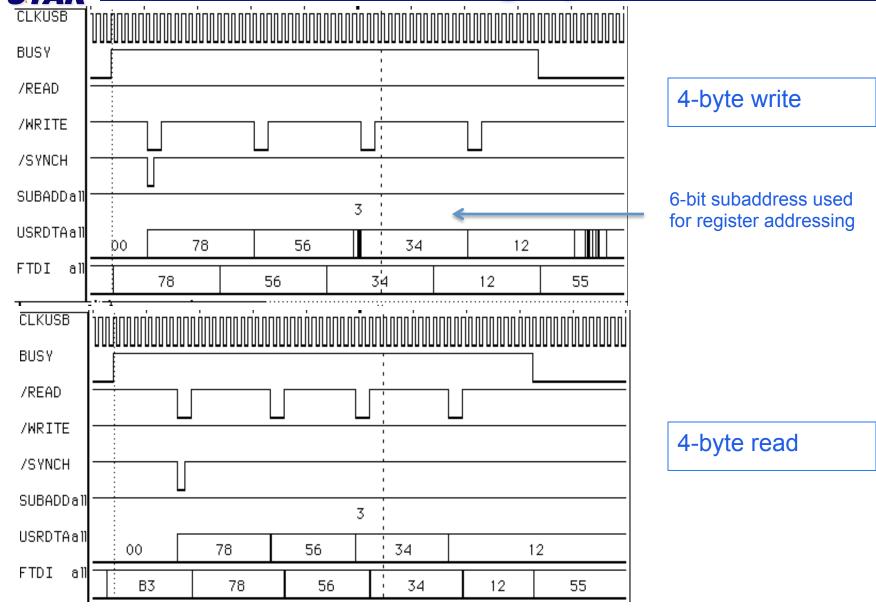

- Orsay USB protocol implemented

- Message layer on top of byte pipe

- Goal: replace VME (4-byte messages)

- Problems

- Bad synthesis by Synopsys tool !!

- Now resolved

- Message protocol working

## USB message protocol

M.J. LeVine BROO

STAR

BROOKHAVEN NATIONAL LABORATORY

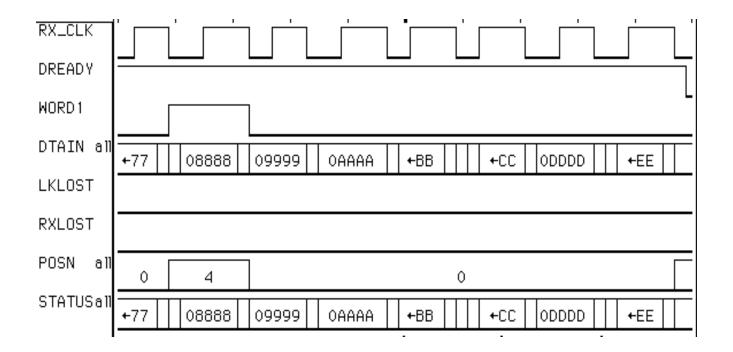

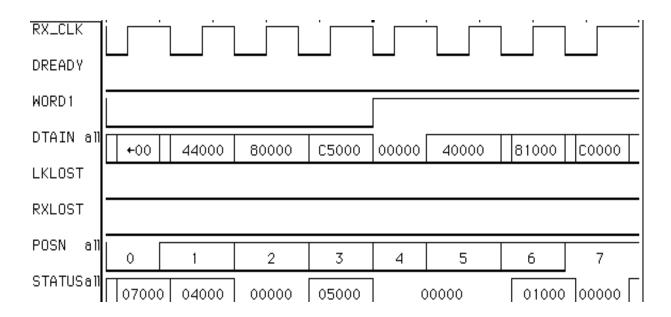

# Testing ladder card with QRDO

BROOKHAVEN NATIONAL LABORATORY

- Generate test patterns on ladder card

- Spy at QRDO on incoming data via fiber with logic analyzer

DREADY='1' signifies data phase Data shown here are artificial for diagnostics

M.J. LeVine BROOKHAVEN NATIONAL LABORATORY

# **Status words received in QRDO**

| <u>Word</u> | <u>Value</u> | Comment (from Table 52, master document)             |  |

|-------------|--------------|------------------------------------------------------|--|

| 0           | 07000        | configured, OK, serdes clock used                    |  |

| 1           | 04000        | deserializer lock OK                                 |  |

| 2           | 00000        | (no optical transceiver problems)                    |  |

| 3           | 05000        | usb present, debug present                           |  |

| 4           | 00000        |                                                      |  |

| 5           | 00000 ]      | actice #1 (careas with bardware assignment on board) |  |

| 6           | 01000 _      | serial #1 (agrees with hardware assignment on board) |  |

| 7           | 00000        | ladder 0 (not yet assigned by QRDO)                  |  |

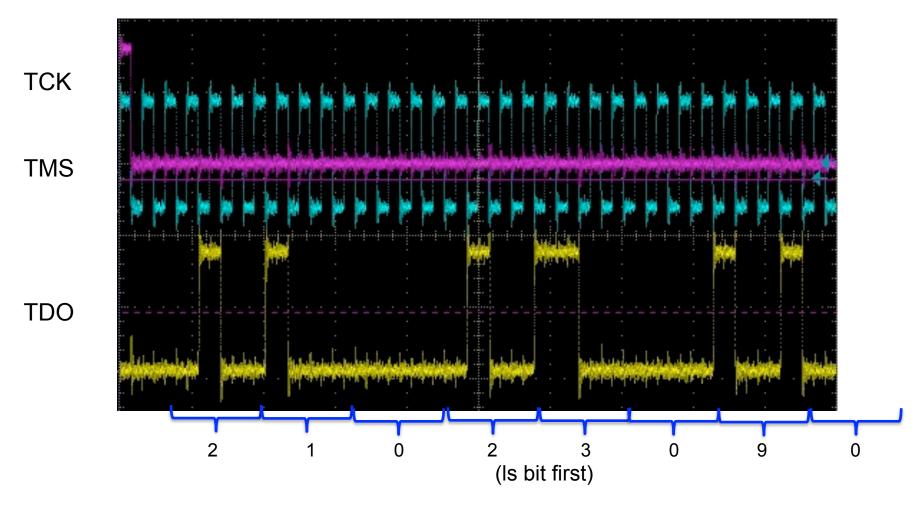

# JTAG testing via fiber

Read version date register (contents = 0x09032012)

M.J. LeVine

BROOKHAVEN NATIONAL LABORATORY

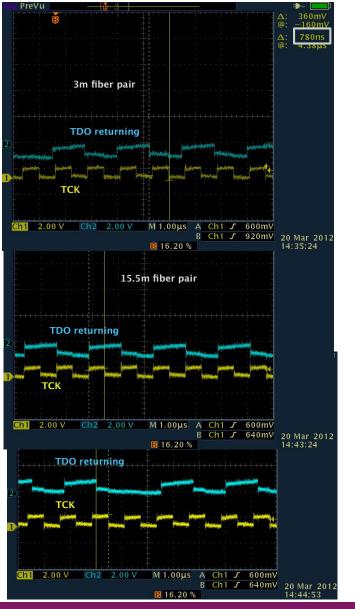

# **Test JTAG with full fiber length**

←

←

1m

15.5m

Returning TDO is shifted on falling edge of TCK. → There is still a safety margin of 480ns with 31m fiber cable.

Note  $\Delta$ =780ns with 3m cable, 600ns with 15.5m cable, 480ns with 31m cable.

(scope probes were not properly grounded, thus shifting baselines)

M.J. LeVine

SSD electronics review, June 20, 2012

31m

- Hardware working as expected – PCB layout by Phil Kuczewski

- Firmware status:

- JTAG to ladder via fiber

- working

- Configure ladder FPGA over fiber

- working

# QRDO (RDO prototype)

- Status

- Have been working with assembled QRDO since Summer 2011

- Uses USB as control port

- Not without problems!

- Allowed verification of data arriving via fiber

- Allowed JTAG to be debugged and verified

- Allowed configuration of ladder FPGA to be debugged and verified

- Download FPGA code via fiber in 0.5s

# RDO

M.J. LeVine BROOKHAVEN NATIONAL LABORATORY SSD electronics review, June 20, 2012

U.S. DEPARTMENT OF ENERGY

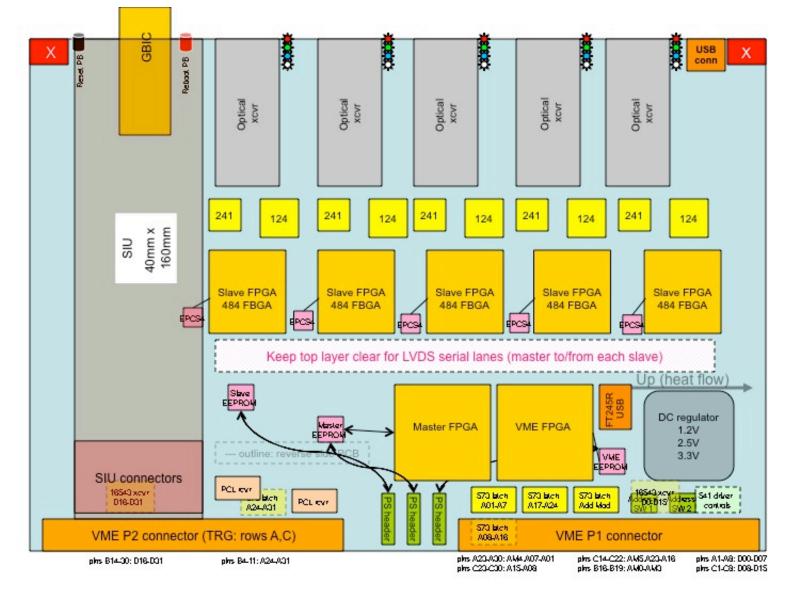

- Schematic complete

- PCB layout finished June 13, 2012

- Assembled prototypes expected mid July, 2012

- need VME master to test complete functionality

Use USB-VME bridge (Wiener)

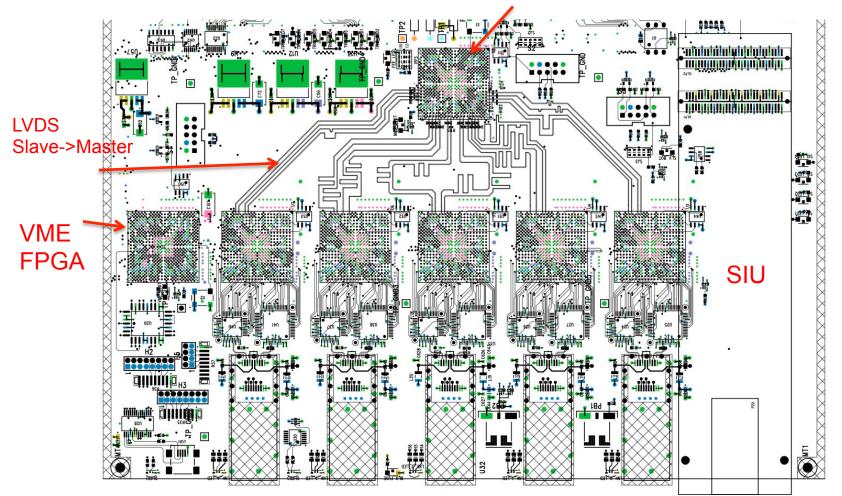

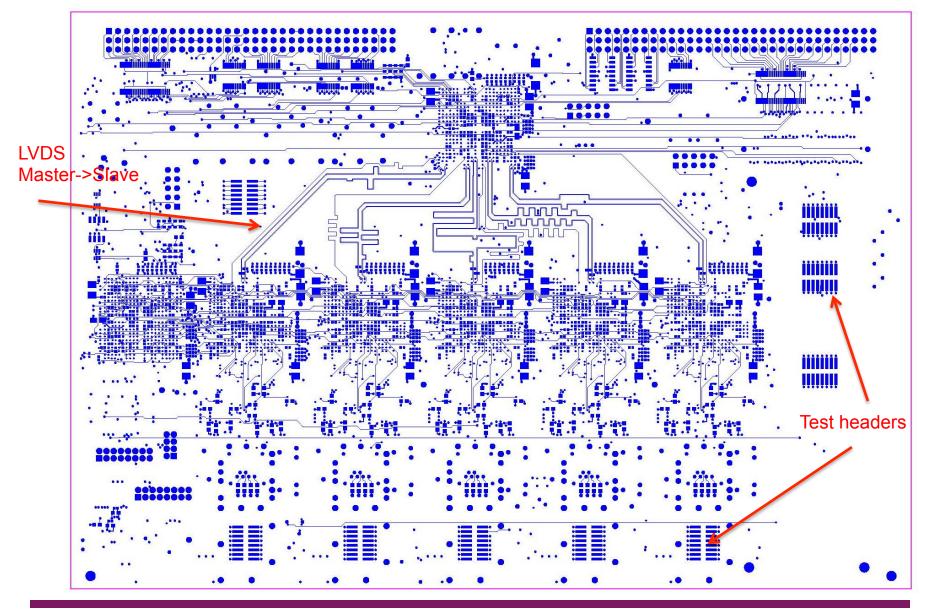

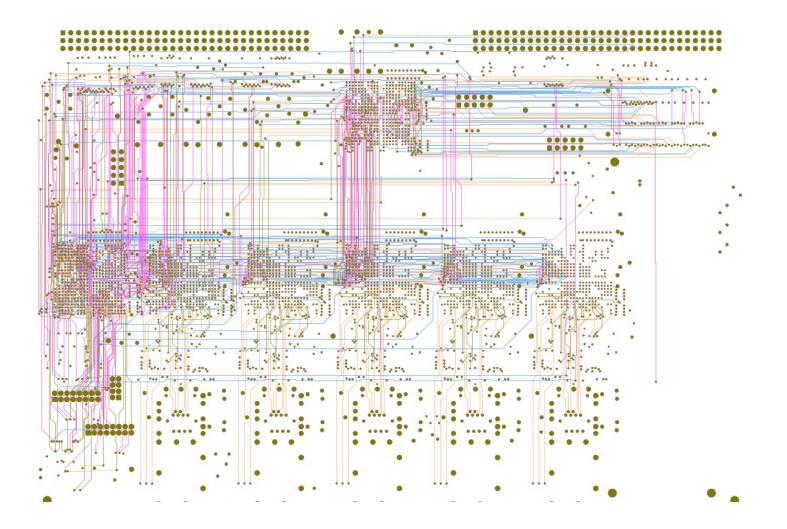

Design uses lvds serial lanes

RROOKHAVEN

M.J. LeVine

- 4 slave -> master (event data)

- 2 master -> slave (commands)

- 5 slaves -> master required 5 PLLs in master

- Only 4 PLLs available in this chip family

M.J. LeVine

- Parallel bus

- High freq clock to have required data xfer rate

- Daisy chained highway

- Too many pins required on slaves

- Large enough FPGA to implement 5 slaves + master

- Not an option until one month ago

- Workaround chosen:

- Source synchronous using clock distributed by master

- Clock captured by slave PLLs and used to transmit to master

- Requires equal round-trip path lengths

- LVDS 454 MHz (2.2ns)

- Path lengths matched to 2.5mm (17 ps) for all 5 slaves

#### **RDO** conceptual layout

# **RDO top layer**

**Master FPGA**

BROOKHAVEN NATIONAL LABORATORY

#### **RDO bottom layer**

M.J. LeVine

BROOKHAVEN NATIONAL LABORATORY

#### **RDO** internal layers

BROOKHAVEN NATIONAL LABORATORY

- 2 DAQ PCs delivered

- 2 D-RORCs installed

1 PC only

- Scientific Linux 5.x installed (64 bit)

- DAQ software installed (Tonko) 1 PC

- Currently using as a test bed for USB software

prototype slow controls platform (temporary)

# RDO

- Status

- -6U VME board very tight

- Components in house

- Schematic finished

- Board layout finished

- Schedule

- Board ready for fabrication

- Assembled by mid-July

- Testing in July-August

BROOKHAVEN

NATIONAL LABORATORY

M.J. LeVine

# SSD slow controls roadmap

#### SSD ladder

# JTAG chain possibilities

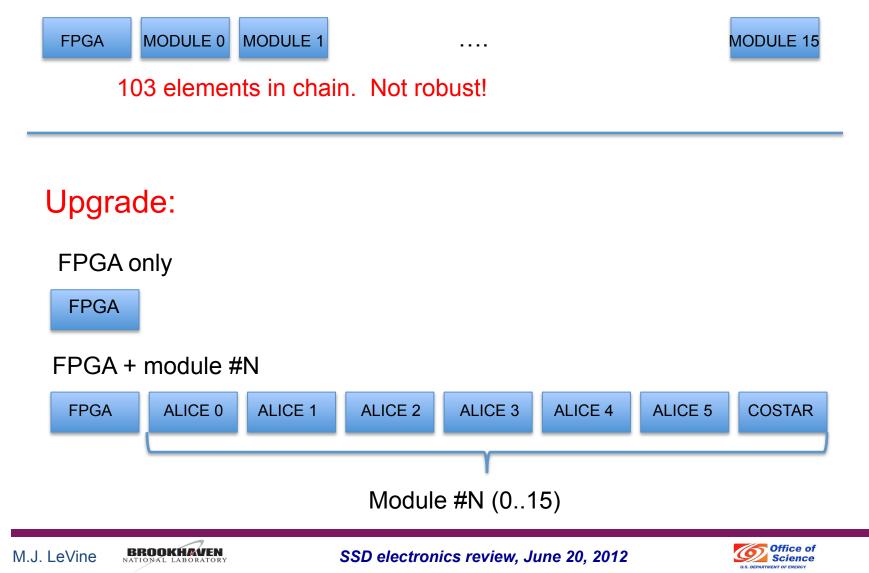

#### Legacy:

FPGA + 16 modules – 7 devices per module !!

# FPGA register configures chain

| 8<br>bits | 1 bit      | 1 level-shifter<br>bit | 1 bit                                        | 1 bit                              | 4 hybrid # bits              |

|-----------|------------|------------------------|----------------------------------------------|------------------------------------|------------------------------|

| free      | HV<br>side | Load DAC channels      | force switchover to use 36.4MHz<br>from xtal | jtag chain with selected<br>hybrid | # of hybrid in jtag<br>chain |

Table 73: ladder-FPGA slow-control register (config)

When "jtag chain with selected hybrid" is asserted, The hybrid selected by "# of hybrid in jtag chain" is included in the JTAG chain.

# Slow controls - layers

- Top level runs on SC linux machine

Identical to previous implementation

- Lower level now a hybrid

- Part on linux VME master

- Part in RDO slave FPGAs

- Interface between these defined 4/12

- Code for lower level written

- Not yet debugged

- Requires a ladder or one module of ladder

# Changes required to slow controls

- Must reconfigure chain each time a module is included/excluded

- Extra steps that were not part of legacy SC software

- Legacy implementation used Corelis VME module

- Based on TI8990 which fills role of JTAG master engine

- Output was multiplexed to 4 Readout boards

- Upgrade JTAG masters implemented in (40) slave FPGAs

- Slow control software must be modified to speak directly to slave FPGAs via VME

- Advantage: 40 macro instructions can be executed simultaneously

# **Existing JTAG implementation**

#### Used for tests --

Function: void write register(reg no, value)

Function: unsigned int read\_register(reg\_no)

Function: void reset\_TAP()

Note – read register implemented as non-destructive (uses circulate data)

# New interface defined (1)

Interface between existing slow controls software (upper level) and the implementation in the slave FPGAs has been negotiated between Weihua Yan and MJL as the following 3 functions which need to be implemented in VHDL and C++:

Function: scan\_ir()

Summary: Scans a bit stream into the TAP instruction register

Usage: void scan\_ir(output, length, input) unsigned short \*output; unsigned short length; unsigned short \*input;

void scan\_ir(unsigned short \*output, unsigned short length, unsigned short \*input) { }

M.J. LeVine

## New interface defined (2)

Function: scan\_dr()

Summary: Scans a bit stream out the TAP data path

Usage: void scan\_dr(output, length, input) unsigned short \*output; unsigned short length; unsigned short \*input;

void scan\_dr(unsigned short \*output, unsigned short length, unsigned short \*input) { }

## New interface defined (3)

Function: circulate\_dr()

Summary: Circulates a bit stream thru the TAP controller data path

Usage: void circulate\_dr(length, data) unsigned short length; unsigned short \*data;

void circulate\_dr(unsigned short length, unsigned short \*output) { }