### HFT mechanical Progress

Wieman RNC LBNL

Jan 2007 DAC review

### Topics, mechanical

- The challenge

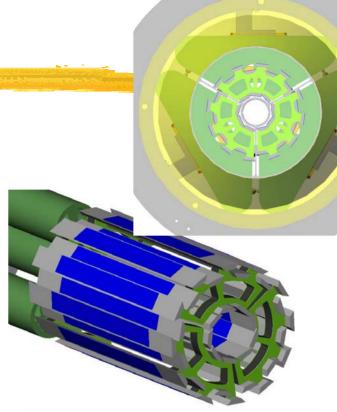

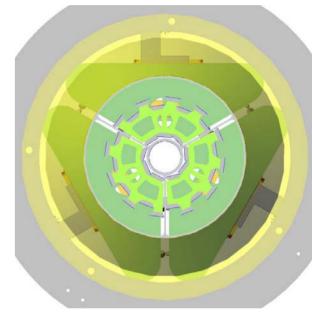

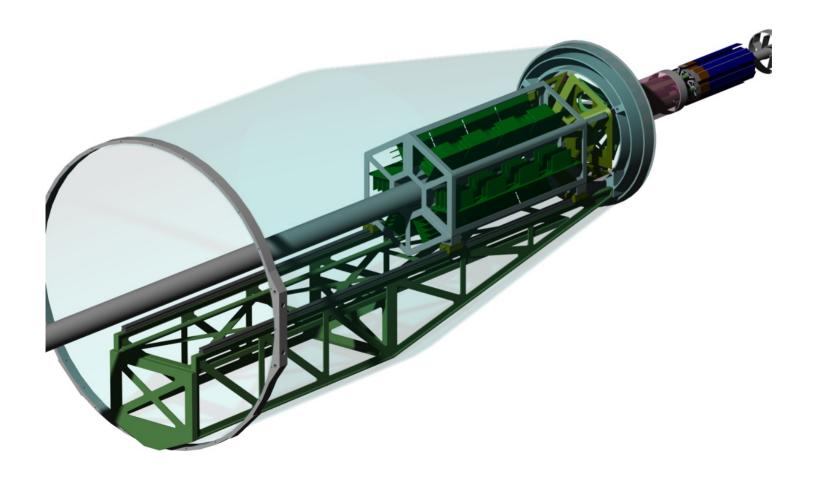

- Mechanical Concept (2 cm beam pipe)

- Simplified concept for support arms

- Thermal studies

- Run 7 MIMOSTAR2 telescope in STAR, mechanical aspects

- v Covered in detail by Michal Szelezniak

- Detector Verification in STAR Environment

- Measure small radius track density

### Some additional electronic issues

- MIMOSTAR 2 Latch up and Upset tests

- Chip development

- Ultra

- The future for pixels, exciting new opportunities

### Some HFT features (the challenge)

| Pointing resolution                | (13 ⊕ 12GeV/p·c) μm           |  |

|------------------------------------|-------------------------------|--|

| Layers                             | Layer 1 at 2.5 cm radius      |  |

|                                    | Layer 2 at 6.5 cm radius      |  |

| Pixel size                         | 30 μ <b>m</b> X 30 μ <b>m</b> |  |

| Hit resolution                     | 8.7 μ <b>m</b>                |  |

| Position stability                 | <b>10</b> μ <b>m</b>          |  |

| Radiation thickness per layer      | X/X0 = 0.28%                  |  |

| Beam pipe radiation thickness      | X/X0 = 0.14%                  |  |

| Number of pixels                   | 135 M                         |  |

| Integration time                   | R&D phase 4 ms                |  |

| (affects pileup)                   | Final detector 0.2 ms         |  |

| Rapid installation and replacement | Reproducible positioning      |  |

### HFT Mechanical requirements

Full self consistent spatial mapping prior to installation

Installation and removal does not disturb mapping

Rapid replacement

10 Micron stability

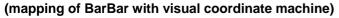

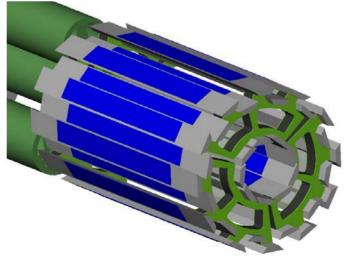

# Conceptual mechanical design

### 2 cm radius beam pipe option

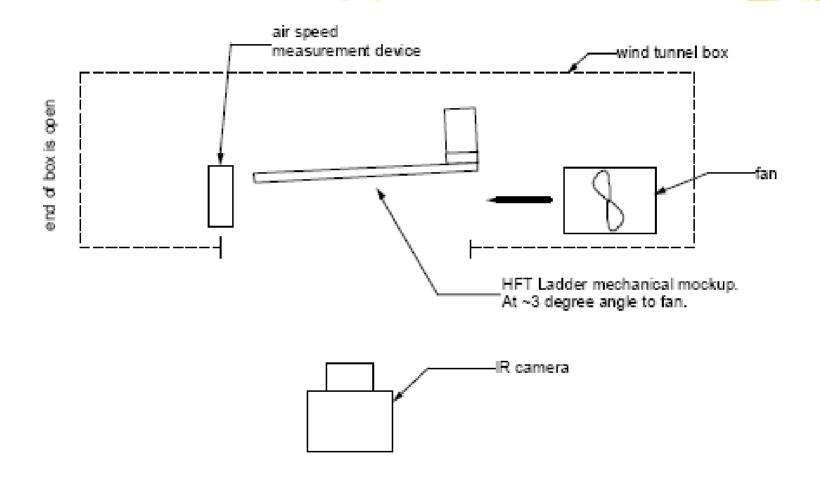

# Thermal, a more comprehensive test confirming older measurements

#### Power on, air cooling 4.5 m/s

Thermal conductivity of silicon is sufficient to get uniform temperature even though a non uniform heating profile was used.

10 °C rise over ambient at 1 m/s air velocity

#### Data

| Airspeed m/s                                  | <u>Temperature</u> |

|-----------------------------------------------|--------------------|

| off (pre-test)                                | 21.016 C           |

| 0.65 m/s                                      | 32.828 C           |

| 1.1 m/s                                       | 31.092 C ●         |

| 2.0 m/s                                       | 30.44 C            |

| 3.5 m/s                                       | 28.288 C           |

| 4.5 m/s                                       | 27.24 C            |

| off (after test)                              | 21.344 C           |

| 0 (larger heater on at 80mW/cm <sup>2</sup> ) | 53 C               |

### Mechanical effort

- Still no serious mechanical engineering effort this last year.

- Negotiating to bring in outside composite engineering capability

- Would very much like ATLAS pixel effort to complete so that we can bring home the LBNL mechanical engineering talent and expertise in composite design to help us

- This year we focused our effort (including mechanical) on MIMOSTAR2 telescope for beam tests

### Planned beam test with 3 chip MIMOSTAR 2 Telescope

- This has been the main program this year

- Purpose

- Develop electronics

- Measure STAR environment close to the beam

- Some associated mechanics

Test MIMOSTAR-2 at the BNL SEU Tandem Facility, latch up and single event upset

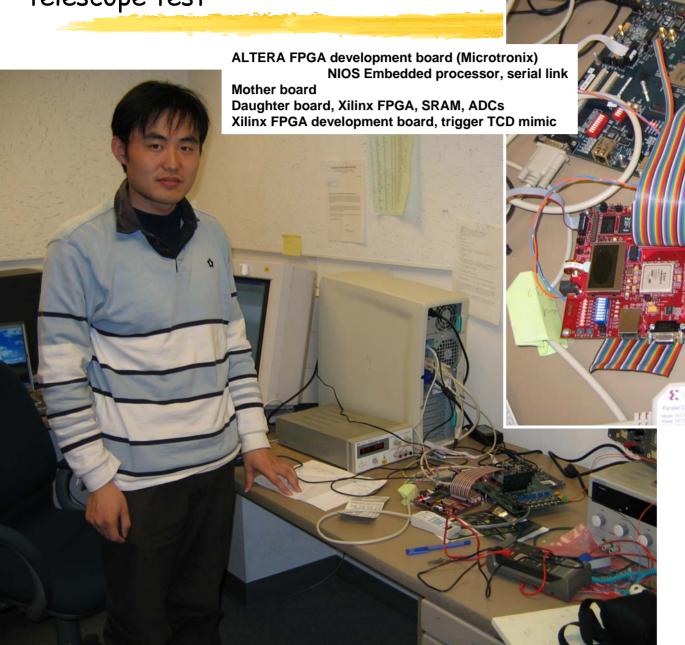

# Readout development, run 7 telescope test

Leo Greiner

Xiangming Sun

Michal Szelezniak

Chinh Vu

Thorsten Stezelberger

(Fred Bieser)

(Robin Gareus)

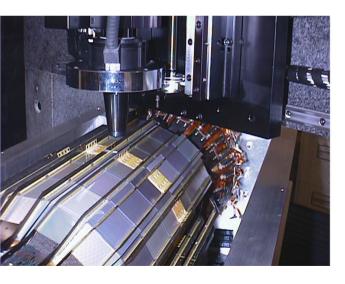

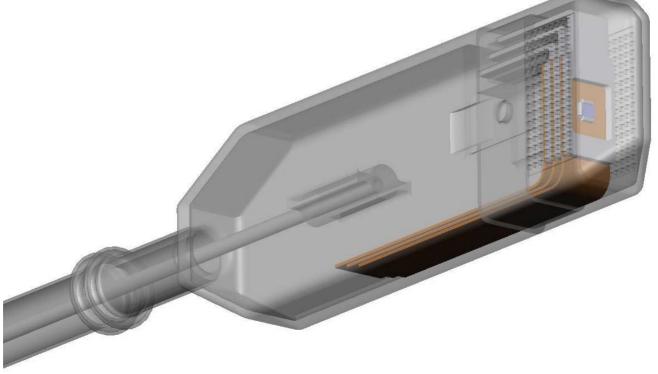

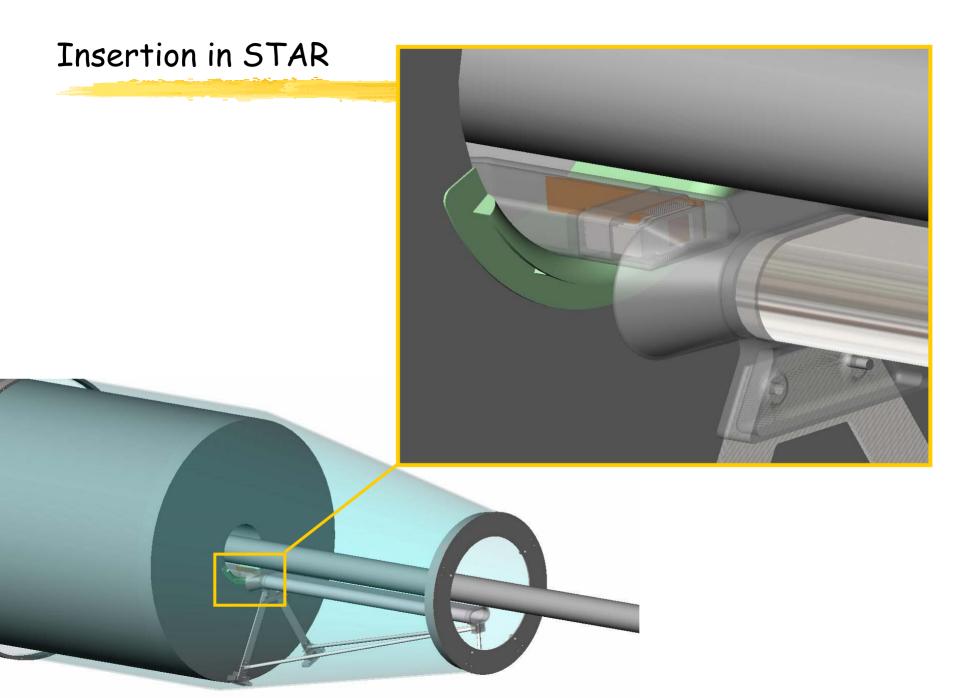

### MIMOSTAR2 Telescope, Run 7 STAR test

- 3 MIMOSTAR2 chips mounted as close together as reasonably possible

- Insertable close to the beam line within 60 cm of the interaction point

- Measure STAR track densities

- Test MIMOSTAR technology

- Test DAQ/TRIGGER system for HFT

### Latch up tests

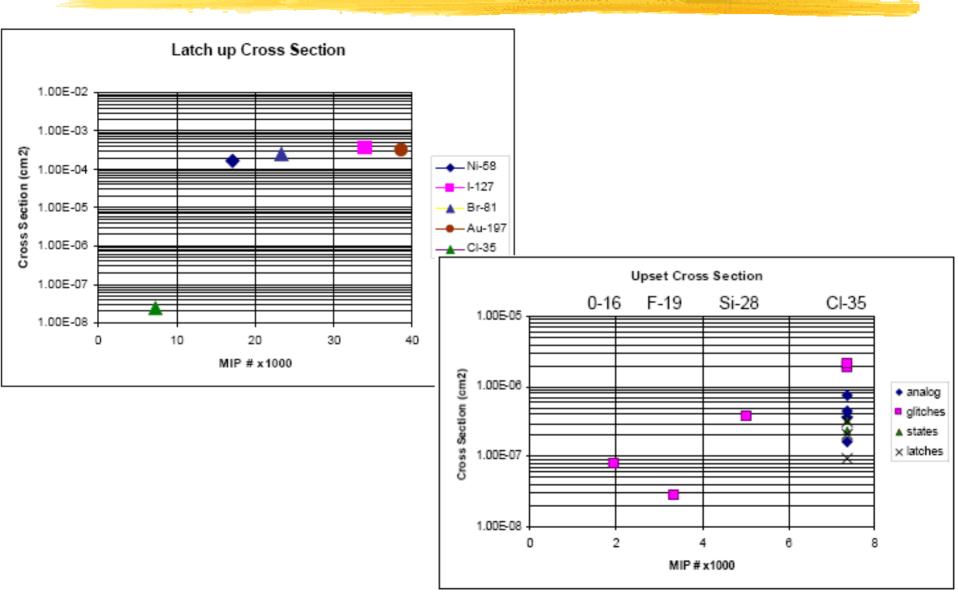

#### Description and Results of latch up tests May 24, 25 2006

#### Contact persons:

Howard Wieman <u>HHWieman@lbl.gov</u>

Leo Greiner <u>LCGreiner@lbl.gov</u>

Michal Szelezniak <u>Michal Szelezniak@ires.in2p3.fr</u>, <u>MASzelezniak@lbl.gov</u>

#### Index

| The goal          | 2 |

|-------------------|---|

| Place             |   |

| Test setup        |   |

| Testing Procedure |   |

| Running the Test  |   |

| Conclusions       |   |

#### List of figures

| Figure 1 SEUTF at BNL. The MimoStar2 test setup is visible in the front. Visible in the |   |

|-----------------------------------------------------------------------------------------|---|

| back is vacuum chamber open to allow fixing the device under test                       | 2 |

| Figure 2 The architecture of the test setup                                             | 5 |

| Figure 3 Detailed schematic of all hardware connections and the daughter card           |   |

| modification                                                                            | Ć |

| Figure 4 Latch up cross sections measured in function of LET (upper plot) and           |   |

| corresponding number of MIPs (lower plot)                                               | 8 |

| Figure 5 Non-latch up upset cross sections measured in function of LET (upper plot) and | į |

| corresponding number of MIPs (lower plot)                                               | 9 |

#### List of tables

- Tests of MIMOSTAR 2

- Facility: SEUTF at BNL, tandem

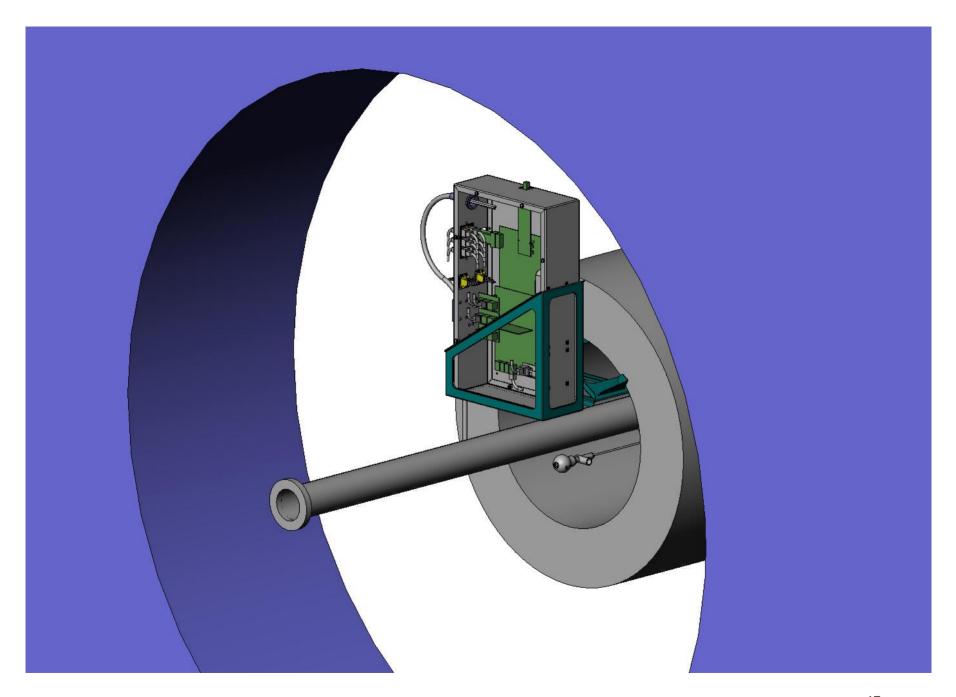

Figure 1 SEUTF at BNL. The MimoStar2 test setup is visible in the front. Visible in the back is vacuum chamber open to allow fixing the device under test.

1

### Latch up and upset results

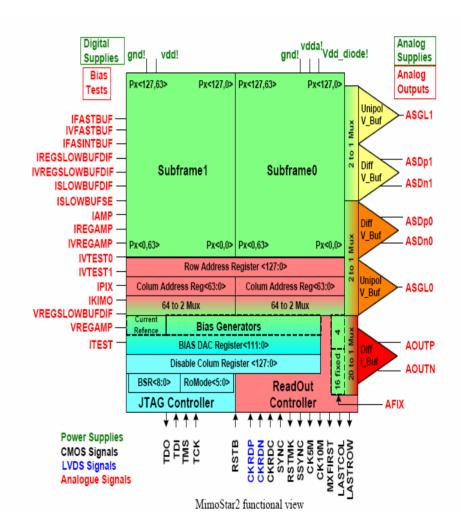

### IPHC/IReS MIMOSTAR chips

- MIMOSTAR1 (0.25 μm TSMC)

- Reduced size prototype but sophisticated chip with complete functions for operation in a real detector system

- Everything operating except pixel signal because of 0.25 μm TSMC feature: Unexpected short signal decay time compared to theory and AMS experience.

- MIMOSTAR2(0.35 μm AMS optical process)

- v Tested in beam

- υ 700-800 e most probable for Min-I

- υ 10-12 e-rms, noise.

- Signal decay time 100 ms

### Ultimate (fast APS detector) - good for high luminosity at RHIC

Submitted requirements list to IReS/IPHC.

In discussion

| Ladder active area                                              | 2cm × 20cm              |

|-----------------------------------------------------------------|-------------------------|

| Pixel size                                                      | 30μm × 30μm             |

| ~Pixel mapping on the ladder                                    | 640 × 6400              |

| Minimum operating distance from beam                            | 1.5 cm                  |

| Power                                                           | ≤100 mW/cm <sup>2</sup> |

| Operating temperature                                           | ≥30 °C                  |

| Integration time[1]                                             | ≤0.2 ms                 |

| Mean silicon thickness                                          | ≤100μm                  |

| Readout time                                                    | ≤1 ms                   |

| Efficiency (min I)[2]                                           | ≥98%                    |

| Accidental cluster density                                      | ≤50/cm <sup>2</sup>     |

| Binary readout, number of threshold bits[3]                     | 2                       |

| Radiation tolerance [4]                                         | ≥124 kRad               |

| Number of conductors supporting the ladder (10 chips/ladder)[5] | ≤140                    |

| Triggered readout, maximum trigger delay[6]                     | 2 μs                    |

#### **Technology MIMOSA8**

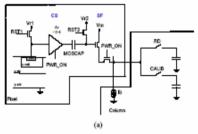

A Fast Monolithic Active Pixel Sensor with Pixel Level Reset Noise Suppression and Binary Outputs for Charged Particle Detection

Yavuz Değerli, Member, IEEE, Grzegorz Deptuch, Member, IEEE, Nicolas Fourches, Member, IEEE,

Abdelkader Himmi, Yan Li, Pierre Lutz, and Fabienne Orsini

Abstract—In order to develop precision vertex detectors for the future linear collider, fast active monolithic active pixel sensors are studied. Seandard CMOS 0.25 µm digital process is used to design a test chip which includes different pixel types, columnlevel discriminators and a digital courtor part. In-pixel amplification it implemented together with double sampling. Different charge-to-voltage conversion factors: were obtained using amplifiers with different gains or diode size. Pixel architectures with DC and AC coupling to charge sensing element were proposed. At far, his from conversion of "Fe-photons were registered for the DC-coupled pixel. Double sampling it functional and allows almost a complete cancellation of fixed pattern notice.

#### I. INTRODUCTION

TN the next generation of linear colliders required for I feature high energy physics experiments, such as the Next Linear Collider (NLC), the Japanese Linear Collider (JLC) and the TeV Energy Superconducting Linear Accelerator (TESLA), precise vertex detectors will be necessary to study the Higgs mechanism. Secondary vertex measurements make a high-resolution vertex detector a necessary part of the detecting system. Precision vertex measurements will be a step forward. Improvements in the spatial resolution are requested making the use of Active Pixel Sensors (APS) an attractive alternative to Hybrid Pixel Sensors (HPS), chosen for the forthcoming Large Hadron Collider (LHC) experiments, both in terms of electronic/detector integration and material thickness. Precision vertex measurements will be a requirement. There has been significant progress done by the IReS/LEPSI-Strasbourg group in the use of the monolithic active pixel sensors (MAPS) for the detection of Minimum Ionizing Particles (MIP) [1]. An array of active sensors with a readout circuitry is integrated in a monolithic structure of a silicon chip. These seasors are designed with standard CMOS technology and have significant advantages over Charge Coupled Devices (CCDs). Two exemplary strong points of MAPS are the high radiation hardness and the flexibility of the readout architecture design. In this paper the chip design with new all-NMOS pixel architectures with integrated correlated double sampling (CDS), suitable for charged particle detection is presented.

Fig. 1. (a) Sobematic of the proposed DC-coupled pixel and, (b) related timing (clocking stimuli) with  $f_{\rm CC}$ =100 MHz. RD, CALIB and LATCH signals are used by the column readout circuitry.

Ö. Deptuch and A. Himmi see with LEPSI and Rics/DN2P3, 23 rue du Losse, 67037 Strabourg Cedex 02, France (e-mail (deptuch, himmi)@lepsi.in2p3.fr).

Y. Değerli, N. Fourches, Y. Li, P. Lutz, and F. Omini are with CEA Saclay, DAPNIA/SEDI and SFP, 91191 Gif-sur-Yvette Cedex, France (e-mail: (degerli, fourches, yanli, latz, crsini)@hep.saclay.cea.fr).

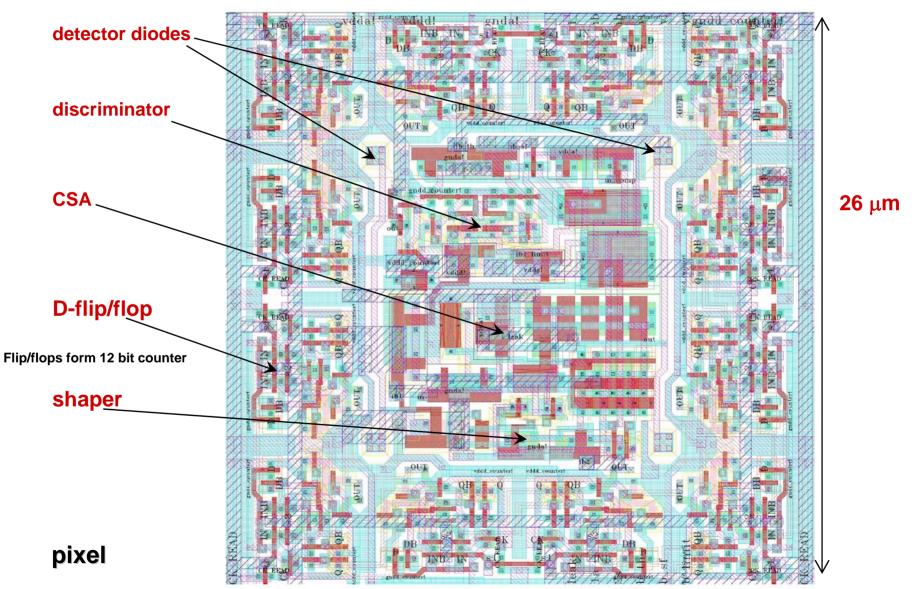

### MIMOSTAR chip development at Strasburg

- MIMOSTAR 1

- full system functionality

- v 4 ms integration

- MIMOSTAR 2

- v full system functionality

- v 4 ms integration

- v 1/25 th reticule

- MIMOSTAR 3 -

- $\nu$  Same as MIMOSTAR 2, but  $\frac{1}{2}$  reticule

- v Engineering run, submitted July 06, foundry will re-run

- MIMOSTAR 4 -

- Same as MIMOSTAR 2 and 3, but full reticule

- υ 640 k pixels

- MIMOSTAR ULTRA

- υ 200 µs integration time

- Based on MIMOSA 8 technology with on pixel analogue storage

### Some material from Grzegorz Deptuch

## Development of 3D Integrated Circuits for HEP

R. Yarema Fermi National Accelerator Lab Batavia, Illinois

12<sup>th</sup> LHC Electronics Workshop, Valencia, Spain September 25-29, 2006

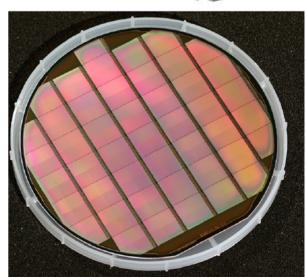

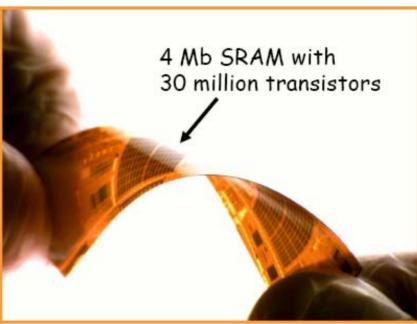

# Thinned SOI Wafers

Wafer thinned to 6 microns and mounted to 3 mil kapton (MIT LL)

### The future is here, Yarmia

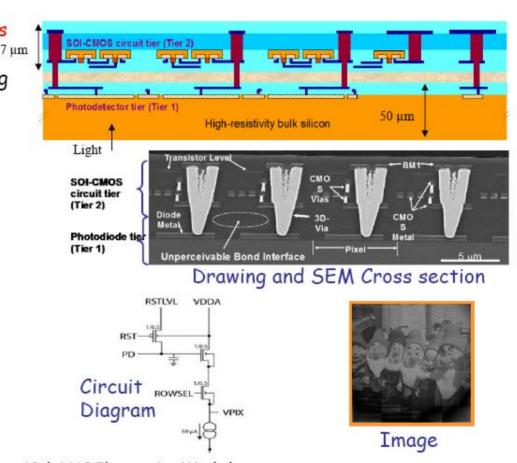

## 3D Megapixel CMOS Image Sensor<sup>8</sup>

- 1024 x 1024, 8 μm pixels

- · 2 tiers

- Wafer to wafer stacking (150 mm to 150 mm)

- 100% diode fill factor

- Tier 1 p+n diodes in >3000 ohm-cm, n-type sub, 50 μm thick

- Tier 2 0.35 um SOI CMOS, 7 μm thick

- 2 μm square vias, dry etch, Ti/TiN liner with W plugs

- Oxide-oxide bonding

- 1 million 3D vias

- Pixel operability >99.999%

- · 4 side abuttable array

12th LHC Electronics Workshop

22

### Yarema

# 3D IC Advantages

- Increased circuit density without going to smaller feature sizes

- ILC demonstrator has 175 transistors in a 20  $\mu$ m pixel

- Unlimited use of PMOS and NMOS transistors

- 100% diode fill factor

- SOI Advantages

- High resistivity substrate for diodes provide large signals

- Minimum charge spreading with fully depleted substrate

- Inherently isolated vias

- 3D may be used to add layers above other sensors types currently under development.

### FERMILAB design in OKI SOI 0.15 mm process

### end