## Research and Development for the HFT at STAR

Leo Greiner

Andrew Rose

Thorsten Stezelberger

Xiangming Sun

Michal Szelezniak \*

Chinh Vu

Howard Wieman

\* IPHC-DRS, Strasbourg, France

Recent progress in hardware and firmware development

### Outline

- Design of the HFT

- Development of the MimoStar family of sensors

- Motivation for the prototype telescope

- Realization of the telescope

- System architecture

- Hardware

- Firmware

- Current status and future plans

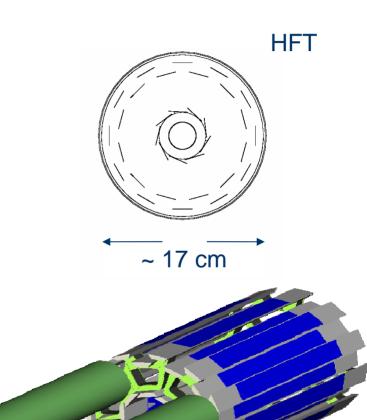

## Design of the HFT

### **Purpose:**

**Greatly improve charm hadron capability in STAR**

#### **Characteristics:**

- Two layers at 2.5 & 7 cm radius (9+24 ladders)

- 0.28 % radiation length/layer

- air cooled

- Active Pixel Sensors

- thinned to 50 µm thickness

- 30 μm x 30 μm pixels

- ~135 M pixels

### MAPS development @ IPHC, Strasbourg for the STAR Upgrade

- JTAG controlled (internal reference voltages and currents set with integrated DACs)

- Serial data readout @ high frequency (we are using 50 MHz)

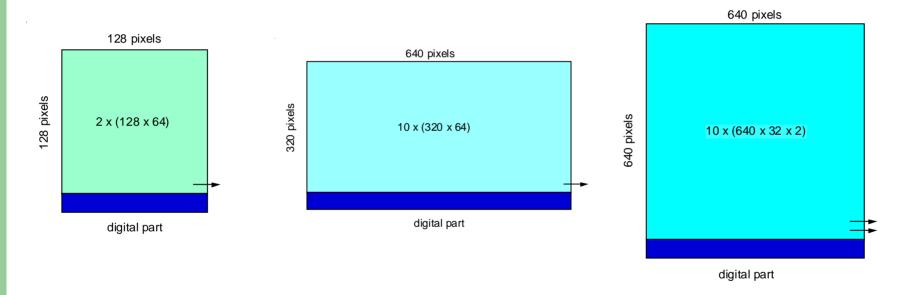

|                      | MimoStar 2      | MimoStar3    | MimoStar4                              |

|----------------------|-----------------|--------------|----------------------------------------|

| Sent for Fabrication | June 2005       | June 2006    | (?)                                    |

| Pixels               | 128 × 128       | 320 × 640    | 640 × 640                              |

| Sub arrays           | 2 + 8 virtual   | 10           | 20                                     |

| Goal                 | validate design | assess yield | for the detector with 4ms readout time |

# Motivation for the telescope

The telescope is a small prototype and contains all elements easily scalable to meet the requirements of the HFT

# test functionality of a prototype MIMOSTAR2 detector in the environment at STAR 2006-2007:

- Charged particle environment near the interaction region in STAR.

- The noise environment in the area in which we expect to put the final HFT.

- Performance of the MIMOSTAR2 sensors.

- Performance of our cluster finding algorithm.

- Performance of our hardware / firmware as a system.

- Functionality of our tested interfaces to the other STAR subsystems.

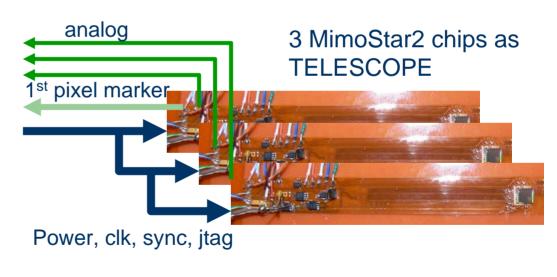

## Realization of the telescope

Control PC (Win)

Analog signals Clock & control JTAG LU prot. Power

**MOTHER BOARD**

Analog signals Clock & control Cluster FIFO Hot Pixel Map Memory Acces (for full frame) Trigger info Power

### DAUGHTER CARD

Trigger, Clock from MWPC

> Power from MWPC

**JTAG** x3 for MIMOSTAR x1 for daughtercard

Latch up monitor and reset

**JTAG**

Trigger, Clock

Busy to trigger

Cluster FIFO

**STRATIX**

serial / ip connection

DDL to Linux PC power

Acquisition Server (Linux)

## Realization of the telescope

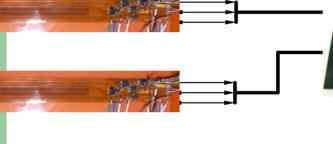

MimoStar2 chips on kapton cables

Analog signals Clock & JTAG LU prot. Powe

**MOTHER BOARD**

Analog signals Clock & control Cluster FIFO Hot Pixel Map Memory Access (for full fram

DAUGHTER CARD

(1) CDS, sorting, CF

(3) Building event

Continuous MimoStar2 readout

(2) TCD trigger

(0) Data acquisition

complex **Hardware** and **Firmware** development

x3 for MIMOSTAR x1 for daughtercard

Latch up monitor and reset

Trigger, Clock Cluster FIFO Busy to trigger

(4) Formatted Event

serial / ip connection

**JTAG**

for this event

(5) Transfer data Linux PQ

Acquisition Server (Linux)

**RORC SIU**

**STRATIX**

# STAR CITT

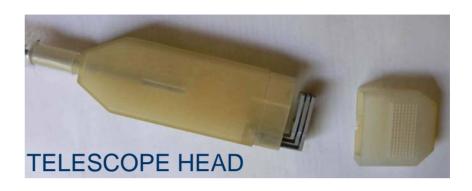

### Hardware - telescope head

Kapton cable:

- •2 Cu layers

- •Thickness 25µm (kapton only)

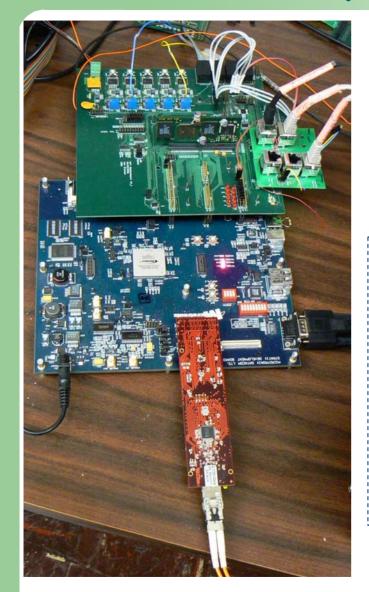

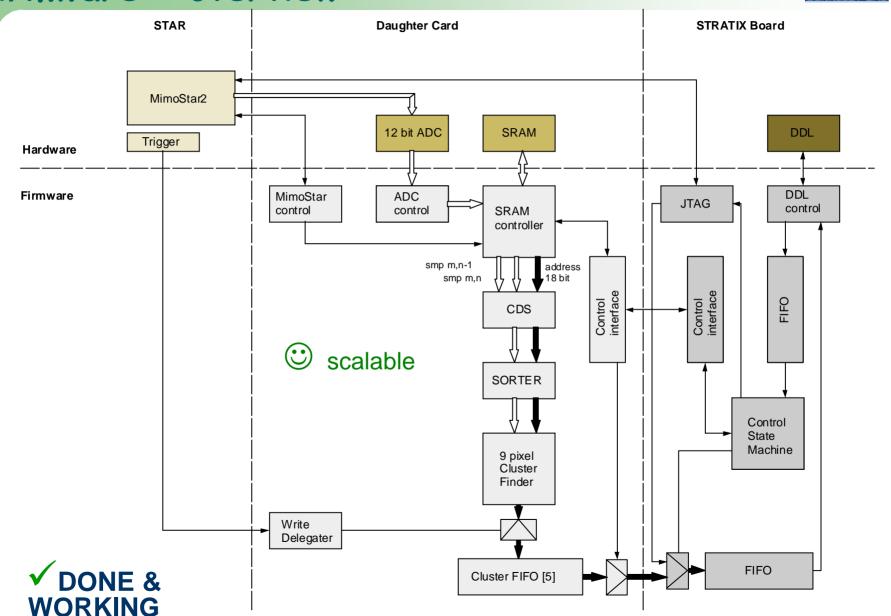

## Hardware components I

Daughter card form the previous stage of development – in the future probably integrated into MB

#### **Mother board**

- Trigger interface to TCD

- Latch up protection on all power supplies

- Remote FPGA programming

#### **Daughter Card**

- √ 50 MHz 12bit ADCs with serial readout

- ✓ SRAM

- Accept and respond to triggers

- ✓ CDS

- Data resorter (because sub-arrays of MimoStar2 are multiplexed for serial readout and reconstruction of arrays is necessary for raster scan is cluster finder module)

- ✓ Cluster finder (slide 12)

- ✓ Cluster FIFO (slide 14)

- ✓ Event builder

# STAR ....

## Hardware components II

#### **STRATIX** development board

- ✓ DDL control interface

- Interface to the control shell (serial port, ethernet)

- ✓ JTAG config for MimoStar2

#### **ALICE DDL-RORC system**

- Optic fiber link to the remote DAQ PC

- ✓ Half duplex connection

- © Part of the DAQ1000 Upgrade

Part accomplished

### Firmware - overview

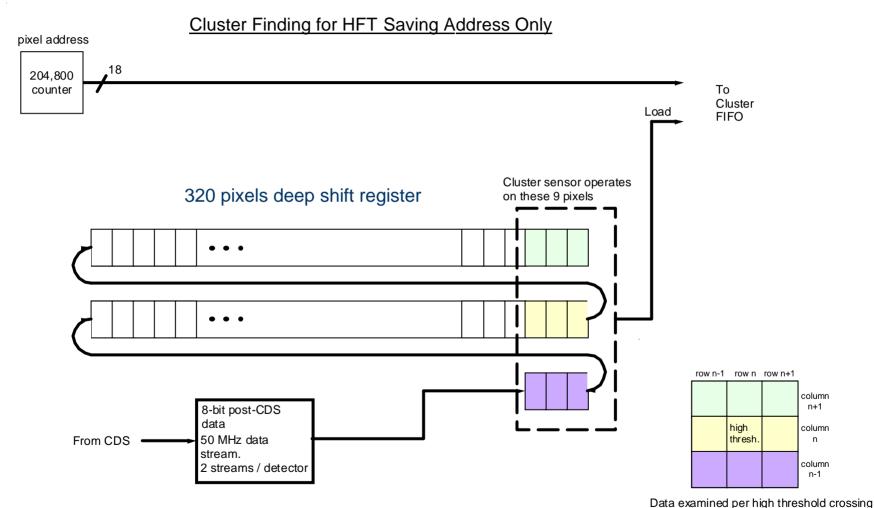

### Firmware - Cluster Finder

on line cluster finding will allow to reduce data flow at HFT by about three orders of magnitude

**✓ DONE & WORKING**

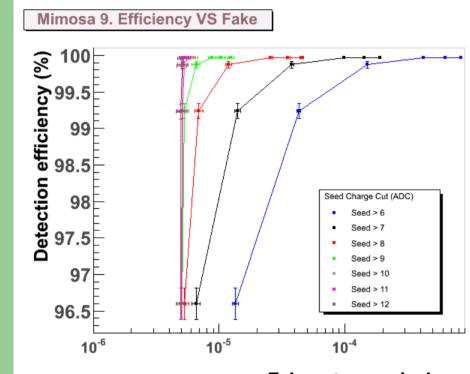

## Firmware - Cluster Finder - efficiency

Fake rate per pixel

By Auguste Besson, IPHC, Strasbourg

- From a prototype in the same technology as MimoStar

- Small diode, pixel pitch 20µm, measured @ 20 °C

- Noise ~10 electrons

- ADC cut on central pixel: 6,7,8,9,10,11,12

- ADC sum of 8 neighbors: 0,3,9,13,17

- Each line fixed central cut, variable cut on neighbors

- Efficiency >99.9 with a fake fate of ~10e-5 is possible

- In reality noise will be higher but a similar efficiency should be achieved for a fake rate below 10e-4

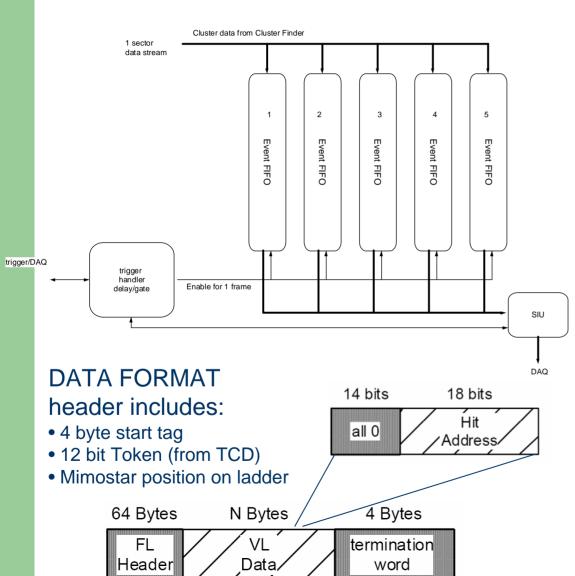

### Firmware - Event builder

- Each Trigger enables an empty Event FIFO for 1 frame (204,800 clocks = 4ms) with an offset to the enable that aligns the event start time with the location of the first pixel in the event.

- Each event FIFO is a separate trigger event stream and can be enabled independently. This allows events to be triggered at ~1 ms intervals with our 4 ms latency.

- Each sector event FIFO is emptied by the SIU at the end of it's triggered frame.

**✓ DONE & WORKING**

FINISH