LG 2005/10/05

Beam Test for Pixel Chips at the ALS 2005

As you are aware, we have a beam test scheduled for the first week in November using 1.5 GeV electrons. We have an experiment inspection scheduled for November 1. Our goal is to have the experimental apparatus ( PC, DAQ boards, chips, etc. ) all up and working on the bench by week of October 17th.

Marco, David and Leo met Ali Belkacem at the ALS to examine the beam line. Ali showed us the area, access points and beam controls. We will all need to be trained in cave entry and exit before we can use the facility. The following pictures show the area and relevant points.

Figure 1: Area on shielding blocks directly above the cave. Note the cable conduit exits next to the column. These give a short (~10') cable run to the beam pipe exit. We can put a table next to the column.

Figure 2: These are the trigger signals from the ALS. The rightmost patch connector labeled "Trig" should provide a TTL signal 80 microseconds before the beam arrival.

Figure 3: The vacuum system is controlled from these panels. We will need training before we can operate this system. If we are running just one setup, we do not need to learn this system and it can be set for us.

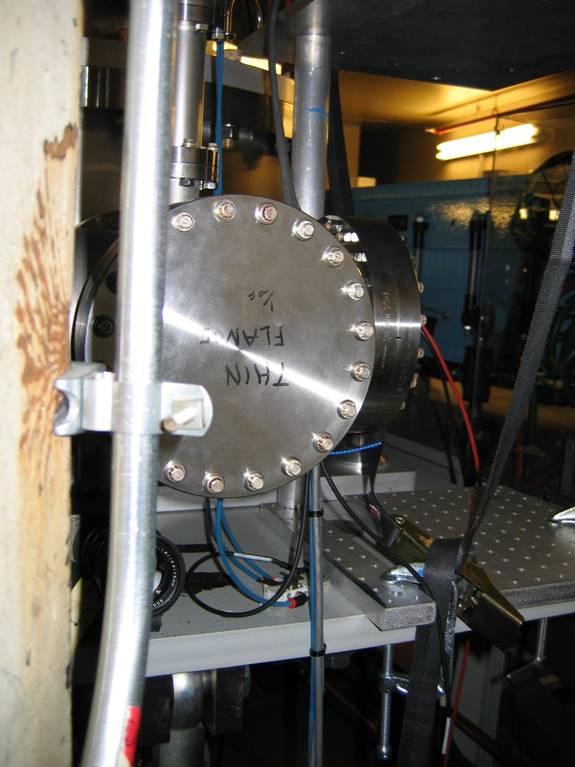

Figure 4: Beam pipe exit in the cave. The flange is a standard 8" conflat which can be removed or replaced. Note the hole plate to the lower right. This allows for easy mounting of electronics / mechanical fixtures. There is also a TV camera to allow viewing of our apparatus.

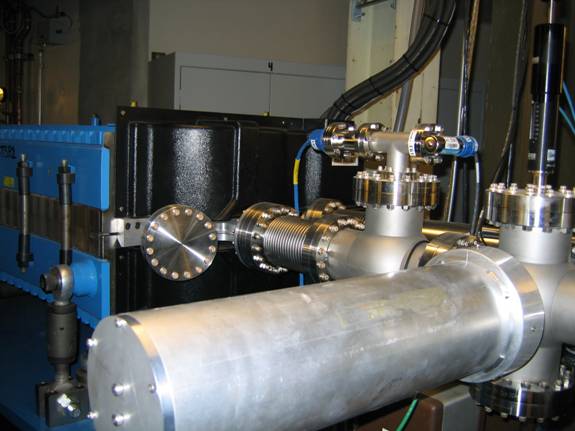

Figure 5: Upstream window of thin Be is located upstream of the bellows. in the foreground is a beam location scintillator and a camera in the aluminum tube.

Figure 6: The exit of the cable conduit and ethernet patch. This area is directly above and adjacent tothe beam exit flange. AC power is also directly available.

Preparation

The tasks as I see them are listed below. Please take a look and let me know what else may be needed.

Expected chips to be tested: MIMOSA5 pre-thinned, APS-4, Martest, Electron Microscopy chip(PD)?

Write VHDL to allow triggered acquisition for all listed chips.

Test VHDL.

Do bench tests of all configurations with pulser trigger simulation of ALS trigger (and LED?) on all hardware that we will use at the ALS.

Mechanical design and fabrication of holders for positioning the chips at the beam exit.

Online software to examine data while we are running.

Storage disks for data.

Training for people who will take data on using the DAQ, etc.

We should meet and develop a run plan, assign responsibilities, and set goals.